# **IQS626A DATASHEET**

Trackpad, ProxFusion® and Hall-Effect Sensor Controller

### **Device overview**

The **IQS626A** ProxFusion<sup>®</sup> IC is a 14-channel multi-sensor controller with best in class sensitivity, signal to noise ratio and power consumption. The device offers either:

- Ultra-low power capacitive wake-up channel with optional associated GPIO output.

- > Hall-effect channel with optional associated GPIO output.

- > A selectable 2x3 or 3x3 mutual-capacitive trackpad.

- > 3 configurable generic ProxFusion® channels, ideal for wear detection with temperature tracking and inductive force sensing.

- > A selection of 4 configurable Reset User Interfaces (RUI) with GPIO outputs for autonomous operation without need for configuration by the master device.

- RUI1

- Self-Capacitive Channel with GPIO3 Output

- o Hall Channel with GPIO4 Output

- Temperature Tracking Channel active for Hall Temperature Compensation

- RUI2

- Self-Capacitive Channel with GPIO3 Output

- Touch-Hold Output on GPIO4

- RUI3

- o I2C Address Strap on GPIO4

- RUI4

- o GPIO4 Forced Active

### Main Features

- > Highly flexible 14-channel ProxFusion® controller.

- Each generic channel can be contabd with three different types of external connections or one of two internal options.

- > 8 external sensor pad connections:

- Self/Mutual-Capacitive sensors

- Self/Mutual-Inductive sensors

- Dedicated reference sensor for environmental / mechanically sensitive designs

- > Internal sensor option:

- Hall-effect sensor

- Temperature sensor

- > Serial scanning (Single ProxFusion<sup>®</sup> engine) up to 14 time-slots

- > Built-in basic functions:

- Automatic tuning

- Noise filtering

WLCSP(1.62x1.62)-16 package

Representation only

- Differential measurements (reference channels)

- Debounce & hysteresis

- Dual direction trigger indication

- Linearization of measurement data

- > Built-in user-interface options:

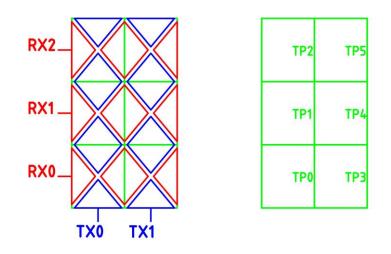

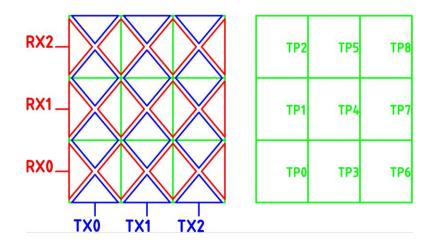

- Trackpad (2x3 or 3x3 projected trackpad setups) with:

- o 2-dimensional coordinate output,

- o axial flick/swipe, tap and hold gesture detection.

- Dedicated ultra-low power channel for power mode handling

- > Wide Range of Capacitance Detection, Wide Electrode Range of 0 to 200pF.

- > Internal sensitivity optimization in high capacitive load conditions.

- > Multiple custom signal level event triggers (e.g. proximity, touch, deep touch).

- > Capacitive resolution: down to 0.02fF

- > Automatic reference channel UI's for temperature and mechanical effects. Assign reference channel to any single or group of channels.

- Options for reduced RF emissions for integration in RF sensitive environments (wide range of charge transfer frequency options).

- > I2C Interface with IRQ (RDY) line

- > A GPIO output which can be associated with the touch state of any channel. Configurable as open-drain, active low (default) or push-pull, active high.

- > Option to configure a GPIO as an address selection pin

- > Hall effect sensor standalone output:

- Product order options for specific power-on GPIO output requirement

- For requirements that range from a single magnet (zero offset) to multiple magnets (field offset present) – e.g. Single magnet docking vs. dual magnet docking

- Power-on options from >10mT magnet changes

- Supply voltage: 1.8V (-2%) to 3.6V

- > Package options: WLCSP-16 (1.62 x 1.62 x 0.5mm), QFN16 (3 x 3 x 0.8mm)

## Applications

- > Hall docking detection.

- > Small form factor trackpads and sliders.

- > Ultra-low power capacitive wake-up and proximity buttons.

- > Wear detection with temperature compensation.

- > Inductive force sensing.

- > Tailored for True Wireless Stereo (TWS) devices.

- Capacitive wake-up, capacitive trackpad/slider, wear detection and magnetic dock detection possible with a single device.

- > Touch area coordinate & multi-button design

- > Electronic keypads or pin pads

## Contents

| DEV    | ICE OVEF                                                 | RVIEW                                                                                                                       | 1  |

|--------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----|

| MAI    | N FEATU                                                  | IRES                                                                                                                        | 1  |

| APP    | LICATION                                                 | ۱۶                                                                                                                          | 2  |

| CON    | TENTS                                                    |                                                                                                                             | 3  |

| 1      | BLOCK                                                    | DIAGRAM                                                                                                                     | 6  |

| 2      | TERMIN                                                   | NAL CONFIGURATION AND FUNCTION                                                                                              | 7  |

| 2      | .1<br>.2<br>.3                                           | WLCSP-16 PIN DIAGRAMS<br>QFN-16 PIN DIAGRAM<br>PIN ATTRIBUTES                                                               | 7  |

| 2      | .4                                                       | SIGNAL DESCRIPTIONS                                                                                                         | 8  |

| 3      | SCHEM                                                    | ATICS, LAYOUT AND COMPONENT SELECTION                                                                                       | 9  |

| -      | .1<br>.2<br>3.2.1<br>3.2.2<br>3.2.3                      | BASIC SCHEMATIC<br>POWER RAIL CAPACITORS<br>Power Supply Capacitors<br>Voltage Regulator Capacitors<br>aCapacitor Selection |    |

| 4      | ELECTR                                                   | ICAL SPECIFICATIONS                                                                                                         |    |

| 4<br>4 | .1<br>.2<br>.3<br>.4<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4 | RECOMMENDED OPERATING CONDITIONS                                                                                            |    |

| 4      | .5<br><i>4.5.1</i>                                       | CURRENT CONSUMPTION                                                                                                         |    |

| 5      | IDENTI                                                   | FICATION                                                                                                                    | 16 |

| 5      | .1<br>.2<br>.3                                           | REVISION IDENTIFICATION<br>WLCSP-16 DEVICE IDENTIFICATION<br>QFN16 DEVICE IDENTIFICATION                                    | 16 |

| 6      | ORDER                                                    | ING INFORMATION                                                                                                             |    |

| 7      | PACKAG                                                   | GE SPECIFICATION                                                                                                            |    |

|        | .1<br>.2                                                 | PACKAGE OUTLINE DESCRIPTION – WLCSP-16<br>PACKAGE OUTLINE DESCRIPTION – QFN-16                                              |    |

| TRA    | NSPAREN                                                  | NT TOP VIEW                                                                                                                 | 19 |

|        | .3<br>.4                                                 | QFN16 RECOMMENDED PCB/FPC FOOTPRINT<br>REFLOW SPECIFICATION                                                                 | 20 |

| 8      |                                                          | ER MAP                                                                                                                      |    |

| 9      |                                                          | ME PROGRAMMABLE BYTES                                                                                                       |    |

| 10     | I <sup>2</sup> C INTE                                    | ERFACE                                                                                                                      | 27 |

| 1  | 0.1              | I <sup>2</sup> C MODULE SPECIFICATION                                 | 27 |

|----|------------------|-----------------------------------------------------------------------|----|

| 10 | 0.2              | I <sup>2</sup> C ADDRESS                                              | 27 |

| 10 | 0.3              | I <sup>3</sup> C                                                      | 27 |

| 10 | 0.4              | I <sup>2</sup> C READ                                                 |    |

| 10 | 0.5              | I2C WRITE                                                             |    |

| 1  | 0.6              | STOP-BIT DISABLE OPTION                                               |    |

| 10 | 0.7              | WATCHDOG TIME-OUT                                                     |    |

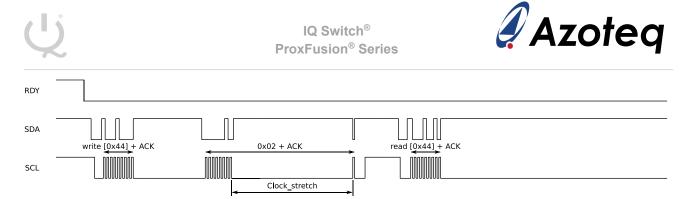

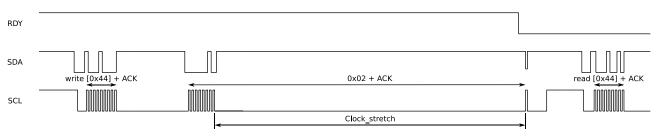

| 10 | 0.8              | CLOCK STRETCHING AND FORCING COMMUNICATIONS                           |    |

|    | 10.8.1           | IQS626A Clock Stretching During a Communication Window (RDY Low)      |    |

|    | 10.8.2           | Clock Stretching When MCU Polls IQS626A Without Waiting for RDY Event |    |

| 11 | SENSOR C         | HANNELS                                                               | 32 |

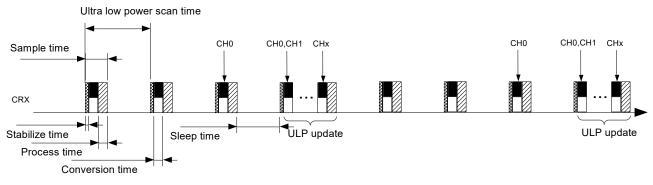

| 1  | 1.1              | ULTRA-LOW POWER CHANNEL                                               | 32 |

|    | 11.1.1           | Channel Outputs                                                       |    |

|    | 11.1.2           | Sensor Modes                                                          |    |

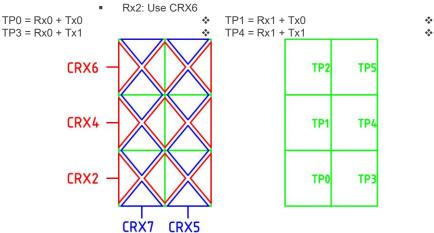

|    | 11.1.3           | CRX Selection                                                         |    |

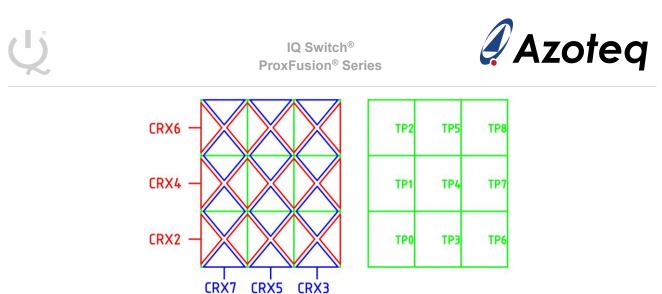

| 1  | 1.2              | MUTUAL-CAPACITIVE TRACKPAD                                            |    |

|    | 11.2.1           | Channel Outputs                                                       |    |

|    | 11.2.2           | Sensor Modes                                                          |    |

|    | 11.2.3           | CRX Selection                                                         |    |

| 1  | 1.3              | Generic Channels                                                      |    |

|    | 11.3.1<br>11.3.2 | Channel Outputs<br>Sensor Modes.                                      |    |

|    | 11.3.3           | CRX Selection                                                         |    |

| 1  | 1.4              | HALL CHANNEL                                                          |    |

| I  | 11.4.1           | Channel Outputs                                                       |    |

|    | 11.4.2           | Sensor Modes                                                          |    |

|    | 11.4.3           | CRX Selection                                                         |    |

| 12 | SPECIAL D        | PEVICE FEATURES                                                       |    |

| 4  | 2.1              | AUTOMATIC TUNING IMPLEMENTATION                                       | 20 |

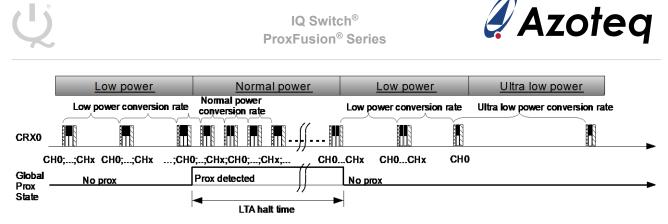

|    | ∠.⊺<br>2.2       | Power Modes                                                           |    |

| 1. | 2.2<br>12.2.1    | Automatic Power Mode Switching                                        |    |

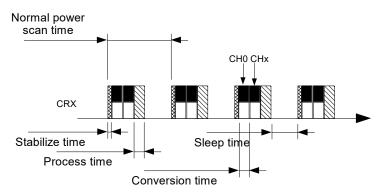

|    | 12.2.1           | Normal Power (NP) Mode                                                |    |

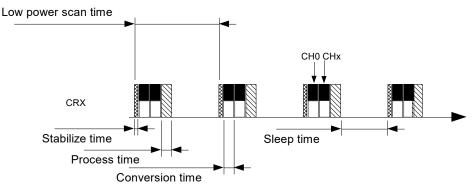

|    | 12.2.2           | Low Power (LP) Mode                                                   |    |

|    | 12.2.4           | Ultra-Low Power Mode                                                  |    |

| 1  | 2.3              | TRACKPAD GESTURES                                                     |    |

|    | 12.3.1           | Тар                                                                   |    |

|    | 12.3.2           | Flick                                                                 |    |

|    | 12.3.3           | Swipe                                                                 |    |

|    | 12.3.4           | Hold                                                                  |    |

| 1: | 2.4              | REFERENCE CHANNELS                                                    | 41 |

|    | 12.4.1           | Reference Channel Reseed UI                                           |    |

|    | 12.4.2           | Reference Channel Tracking UI                                         |    |

| 13 | RESET US         | ER INTERFACES                                                         | 43 |

| 1: | 3.1              | RUI System Settings                                                   | 43 |

|    | 13.1.1           | GPIO Type                                                             |    |

|    | 13.1.2           | Ready Type                                                            |    |

|    | 13.1.3           | I <sup>2</sup> C Address                                              |    |

|    | 13.1.4           | Main Oscillator Frequency                                             |    |

| 1: | 3.2              | SELF-CAPACITIVE CHANNEL WITH GPIO3 OUTPUT                             |    |

|    | 13.2.1           | Self-Capacitive Channel CRX Pins                                      |    |

|    | 13.2.2           | Self-Capacitive Channel Touch Threshold                               |    |

| 1; | 3.3              | HALL CHANNEL WITH GPIO4 OUTPUT                                        |    |

|    | 13.3.1           | Hall Channel ATI Target                                               |    |

| 13.3.2      | Hall Channel Touch Threshold                     | 45 |

|-------------|--------------------------------------------------|----|

| 13.4        | TEMPERATURE TRACKING CHANNEL                     | 46 |

| 13.5        | HALL TEMPERATURE COMPENSATION                    | 47 |

| 13.6        | TOUCH-HOLD OUTPUT ON GPIO4                       | 47 |

| 13.7        | I <sup>2</sup> C Address Strap on GPIO4          | 47 |

| 13.8        | GPIO4 Forced Active                              | 47 |

| APPENDIX A. | DETAILED REGISTER DESCRIPTIONS                   | 49 |

| APPENDIX B. | DETAILED ONE-TIME PROGRAMMABLE BYTE DESCRIPTIONS | 71 |

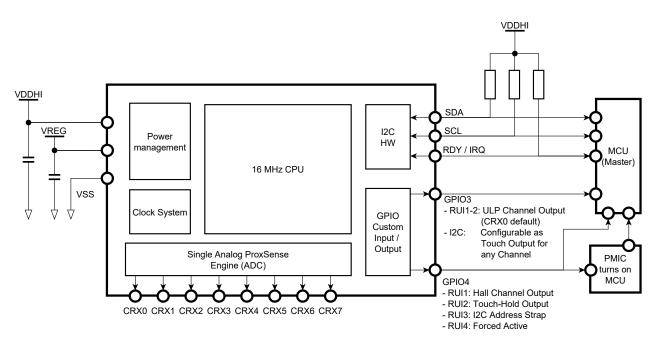

## 1 Block diagram

Figure 1.1: Functional block diagram

## 2 Terminal configuration and function

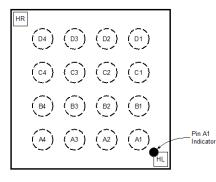

## 2.1 WLCSP-16 Pin diagrams

| Pin no.       | Signal name | Pin no.       | Signal name |

|---------------|-------------|---------------|-------------|

| A1            | CRX6        | C1            | VDDHI       |

| A2            | CRX2        | C2            | GPIO3       |

| A3            | CRX0        | C3            | SDA         |

| A4            | CRX5        | C4            | VSS         |

| B1            | CRX4        | D1            | GPIO4       |

| B2            | CRX1        | D2            | SCL         |

| B3            | CRX3        | D3            | RDY         |

| B4            | CRX7        | D4            | VREG        |

|               |             |               |             |

| Area name     | Signal name | Area name     | Signal name |

| HR (internal) | HALL RIGHT  | HL (internal) | HALL LEFT   |

### Figure 2.1: 16-pin WLCSP package (Top view)

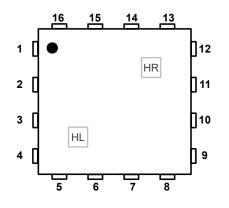

### 2.2 **QFN-16 Pin diagram**

| Pin no.       | Signal name | Pin no.       | Signal name    |

|---------------|-------------|---------------|----------------|

| 1             | GPIO3       | 9             | CRX3           |

| 2             | GPIO4       | 10            | CRX5           |

| 3             | VDDHI       | 11            | CRX7           |

| 4             | CRX6        | 12            | VSS            |

| 5             | CRX4        | 13            | VREG           |

| 6             | CRX2        | 14            | RDY            |

| 7             | CRX1        | 15            | SDA            |

| 8             | CRX0        | 16            | SCL            |

|               |             | 17            | TAB - floating |

|               |             |               |                |

| Area name     | Signal name | Area name     | Signal name    |

| HR (internal) | HALL RIGHT  | HL (internal) | HALL LEFT      |

|               |             |               |                |

Figure 2.2: 16-pin QFN package (Top view)

#### 2.3 **Pin attributes**

| Pin no. |       | Signal name | Signal type <sup>1</sup> | Buffer type | Power source | Reset state after BOR <sup>2</sup> |

|---------|-------|-------------|--------------------------|-------------|--------------|------------------------------------|

| WLCSP16 | QFN16 |             |                          |             |              |                                    |

| A1      | 4     | CRX6        | Analog                   | LVCMOS      | VREG         | High-Z                             |

| A2      | 6     | CRX2        | Analog                   | LVCMOS      | VREG         | High-Z                             |

| A3      | 8     | CRX0        | Analog                   | LVCMOS      | VREG         | High-Z                             |

| A4      | 10    | CRX5        | Analog                   | Analog      | VREG         | High-Z                             |

| B1      | 5     | CRX4        | Analog                   | LVCMOS      | VREG         | High-Z                             |

| B2      | 7     | CRX1        | Analog                   | LVCMOS      | VREG         | High-Z                             |

| B3      | 9     | CRX3        | Analog                   | LVCMOS      | VREG         | High-Z                             |

| B4      | 11    | CRX7        | Analog                   | Analog      | VREG         | High-Z                             |

| C1      | 3     | VDDHI       | Р                        | Power       | N/A          | High-Z                             |

| C2      | 1     | GPIO3       | 0                        | LVCMOS      | VDDHI        | High-Z                             |

| C3      | 15    | SDA         | I/O                      | LVCMOS      | VDDHI        | High-Z                             |

| C4      | 12    | VSS         | Р                        | Power       | N/A          | High-Z                             |

| D1      | 2     | GPIO4       | I/O                      | LVCMOS      | VDDHI        | High-Z                             |

| D2      | 16    | SCL         | I/O                      | LVCMOS      | VDDHI        | High-Z                             |

| D3      | 14    | RDY         | I/O                      | LVCMOS      | VDDHI        | High-Z                             |

| D4      | 13    | VREG        | 0                        | Power       | VDDHI        | High-Z                             |

|         | 17    | TAB         | Floating                 | N/A         | N/A          | N/A                                |

<sup>1</sup> Signal Types: I = Input, O = Output, I/O = Input or Output

<sup>2</sup> High-Z = High-impedance with Schmitt trigger and pullup or pulldown (if available) disabled

Copyright © Azoteq 2020 All Rights Reserved

## 2.4 Signal descriptions

| Function                | Signal name | Pin no. |       | Pin type | Description                                                                                    |  |  |

|-------------------------|-------------|---------|-------|----------|------------------------------------------------------------------------------------------------|--|--|

|                         |             | WLCSP16 | QFN16 |          |                                                                                                |  |  |

| ProxFusion <sup>®</sup> | CRX6        | A1      | 4     | I/O      | ProxFusion <sup>®</sup> channel                                                                |  |  |

|                         | CRX2        | A2      | 6     | I/O      |                                                                                                |  |  |

|                         | CRX0        | A3      | 8     | I/O      |                                                                                                |  |  |

|                         | CRX5        | A4      | 10    | I/O      |                                                                                                |  |  |

|                         | CRX4        | B1      | 5     | I/O      |                                                                                                |  |  |

|                         | CRX1        | B2      | 7     | I/O      |                                                                                                |  |  |

|                         | CRX3        | B3      | 9     | I/O      |                                                                                                |  |  |

|                         | CRX7        | B4      | 11    | I/O      |                                                                                                |  |  |

| GPIO                    | GPIO4       | D1      | 2     | I/O      | Custom Output (HALL, Touch&Hold, Forced high on reset) / Address input (high: 0x44, low: 0x45) |  |  |

|                         | GPIO3       | C2      | 1     | 0        | Custom Touch Out                                                                               |  |  |

| I <sup>2</sup> C        | SCL         | D2      | 16    | I/O      | l <sup>2</sup> C clock                                                                         |  |  |

|                         | SDA         | C3      | 15    | I/O      | I <sup>2</sup> C data                                                                          |  |  |

|                         | RDY (IRQ)   | D3      | 14    | 0        | I <sup>2</sup> C event mode interrupt                                                          |  |  |

| Power                   | VDDHI       | C1      | 3     | Р        | Power supply                                                                                   |  |  |

|                         | VREG        | D4      | 13    | 0        | ProxFusion <sup>®</sup> regulator external decoupling capacitor                                |  |  |

|                         | VSS         | C4      | 12    | Р        | Power ground                                                                                   |  |  |

## 3 Schematics, Layout and Component Selection

### 3.1 Basic Schematic

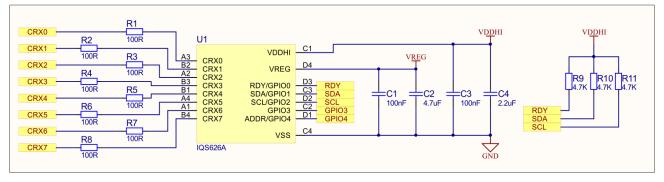

*Figure 3.1* below shows a minimal reference schematic for the most basic of IQS626A applications. Note that the connections of CRX0 through CRX7 will differ substantially for each application. See

Figure 3.1: Reference Schematic

### 3.2 **Power Rail Capacitors**

### 3.2.1 **Power Supply Capacitors**

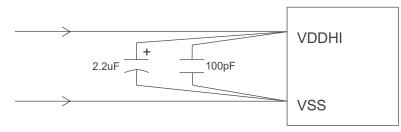

It is recommended to place a  $2.2\mu$ F and 100pF parallel combination of low-ESR ceramic decoupling capacitors between the VDDHI and VSS nets. Higher-value capacitors may be used but can impact supply rail ramp-up time. Decoupling capacitors must be placed as close as possible to the pins that they decouple (within a few millimeters) with the smaller capacitor being the closer than the larger capacitor. Figure 3.2 illustrates this.

Figure 3.2: Recommended power supply capacitors.

### 3.2.2 Voltage Regulator Capacitors

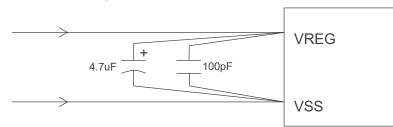

The VREG pin requires at least a  $1\mu$ F capacitor to regulate the LDO voltage regulator internal to the device. It is also recommended to place a 100pF capacitor between VREG and VSS for improved noise immunity. These capacitors should be placed as close to the IC as possible with the smaller capacitor being closer than the larger capacitor. *Figure 3.3* Illustrates this.

Figure 3.3: Recommended voltage regulator capacitors.

### 3.2.3 aCapacitor Selection

In section 3.2.1 and section 3.2.2 it is recommended to place 2 capacitors on between both VDDHI and GND and VREG and GND. In both cases a larger value capacitor and a smaller value capacitor is recommended. The larger value capacitors for VDDHI and VREG are respectively referred to as  $C_{VDDHI}$  and  $C_{VREG}$  in this section. This smaller value capacitors are for noise immunity purposes, the same value should be used for VDDHI and VREG.

### 3.2.3.1 Low Inline-Resistance Power Supplies

For supplies with low in-line resistance and high current output capability is it recommended to ensure that  $C_{VREG} > 2C_{VDDHI}$ . This is to prevent a known ESD risk as explained below.

Known risk: The IQS626A will not recover from ESD events is the following conditions are met:

- > VDDHI source is present with low impedance path and high current sourcing capability

- > C<sub>VDDHI</sub> > C<sub>VREG</sub>

With these conditions met, the source keeps VDDHI above the BOD level during the ESD event but drains the VREG capacitor during sleep mode causing a unique sleep-mode BOD event keeping the IC in reset. This only recovers when forcing a POR on VDDHI.

*Table 3-1* Shows recommended values for  $C_{VDDHI}$  and  $C_{VREG}$  values for power supplies with low inline-resistance.

| Maximum Report | Mini                   | mum                     | Recommended for        | r General Design        |  |

|----------------|------------------------|-------------------------|------------------------|-------------------------|--|

| Rate (ms)      | C <sub>VREG</sub> (μF) | C <sub>vddнi</sub> (µF) | C <sub>VREG</sub> (μF) | C <sub>vddнi</sub> (µF) |  |

| 64             | 2.2                    | 1                       |                        |                         |  |

| 128            | 2.2                    | 1                       |                        | 0.0                     |  |

| 160            | 3.3                    | 1.5                     | 4.7                    | 2.2                     |  |

| 256            | 3.9                    | 1.5                     |                        |                         |  |

Table 3-1: Recommended capacitor values for low inline-resistance power supplies.

### 3.2.3.2 High Inline-Resistance Power Supplies

For supplies with a high in-line resistance (such as battery with high series resistance) it is recommended to ensure that  $C_{VDDHI} > C_{VREG}$  to prevent an unexpected dip on VDDHI when the sensor wakes from sleep-mode and re-charges the VREG capacitor. *Table 3-2* shows recommended capacitor values for power supplies with high inline-resistance.

| Table 3-2: Recommended | canacitor values | for high inline.   | _resistance  | nower supplies  |

|------------------------|------------------|--------------------|--------------|-----------------|

|                        | capacitor values | IOI IIIgii IIIIIIC | -10313141100 | power supplies. |

| Maximum Report | Mini                   | mum                     | Recommended for        | r General Design        |  |

|----------------|------------------------|-------------------------|------------------------|-------------------------|--|

| Rate (ms)      | C <sub>VREG</sub> (µF) | C <sub>VDDHI</sub> (µF) | C <sub>VREG</sub> (µF) | C <sub>vddhi</sub> (µF) |  |

| 64             | 2.2                    | 2.2                     |                        |                         |  |

| 128            | 2.2                    | 2.2                     |                        | 4 7                     |  |

| 160            | 3.3                    | 3.3                     | 4.7                    | 4.7                     |  |

| 256            | 3.9                    | 3.3                     |                        |                         |  |

## 4 Electrical Specifications

## 4.1 Recommended Operating Conditions

#### Table 4-1: Recommended operating conditions.

| Parameter         | Description                                                                          | Min.           | Тур. | Max. | Unit |

|-------------------|--------------------------------------------------------------------------------------|----------------|------|------|------|

| VDDHI             | Supply voltage applied at VDDHI pin                                                  | 1.764          |      | 3.6  | V    |

| VREG              | Regulator output at VREG                                                             | 1.62           |      | 1.7  | V    |

| VSS               | Supply voltage applied at VSS pin                                                    |                | 0    |      | V    |

| T <sub>A</sub>    | Operating free-air temperature                                                       | -40            |      | 85   | °C   |

| CVDDHI            | Recommended capacitor at VDDHI <sup>1</sup>                                          | 1 <sup>2</sup> | 2.2  | 10   | μF   |

| C <sub>VREG</sub> | Recommended external buffer capacitor at VREG, ESR≤ 200mΩ                            | 0.8            | 4.7  | 10   | μF   |

| CELECTRODE        | Maximum capacitance of all external electrodes on all ProxFusion <sup>®</sup> blocks | N/A            |      | 200  | pF   |

## 4.2 Absolute maximum ratings

#### Table 4-2: Absolute maximum ratings.

| Parameter                                            | Min. | Max.                      | Unit |

|------------------------------------------------------|------|---------------------------|------|

| Voltage applied at VDDHI pin to VSS                  | -0.3 | +3.6                      | V    |

| Voltage applied to any ProxFusion <sup>®</sup> pin   | -0.3 | VREG                      | V    |

| Voltage applied to any other pin (referenced to VSS) | -0.3 | VDDHI + 0.3<br>(3.6V max) | V    |

| Storage temperature, T <sub>stg</sub>                | -40  | 125                       | °C   |

### 4.3 Electrostatic Discharge ratings

#### Table 4-3: Electrostatic ratings.

| Parameter          | Description   |                                                                                 | Value | Unit |

|--------------------|---------------|---------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>3</sup>                 | ±4000 |      |

|                    | discharge     | Charged-device model (CDM), per JEDEC specification<br>JESD22-C101 <sup>4</sup> | ±500  | V    |

### 4.4 Timing and switching characteristics

### 4.4.1 Reset levels

#### Table 4-4: Reset levels.

| Parameter              | Description                            | Conditions                       | Min. | Тур. | Max. | Unit |

|------------------------|----------------------------------------|----------------------------------|------|------|------|------|

| $V_{\text{BOR, safe}}$ | Safe BOR power down level <sup>5</sup> | V <sub>DDHI</sub> slope ≥ 100V/s | 0.6  |      |      | V    |

| V <sub>DDHI</sub>      | Power-up/down level (Reset trigger)    | V <sub>DDHI</sub> slope ≥ 100V/s |      |      | 1.7  | V    |

| $V_{\text{REG}}$       | Power-up/down level (Reset trigger)    |                                  |      |      | 1.55 | V    |

## 4.4.2 Miscellaneous timings

#### Table 4-5: Miscellaneous timings.

| Parameter         | Description                                                | Min. | Тур. | Max. | Unit |

|-------------------|------------------------------------------------------------|------|------|------|------|

| f <sub>xfer</sub> | Charge transfer frequency (derived from f <sub>SYS</sub> ) | -2%  |      | +2%  | V    |

#### <sup>1</sup> A capacitor tolerance of ±20% or better is required

<sup>2</sup> The minimum value ensures optimal performance in various low power modes that are possible

$^5$  A safe BOR can be correctly generated only if  $V_{\text{DDHI}}$  drops below this voltage before it rises.

IQS626A Datasheet v1.3 Check for latest datasheet

<sup>&</sup>lt;sup>3</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±4000 V may actually have higher performance.

<sup>&</sup>lt;sup>4</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ±500 V may actually have higher performance.

## 4.4.3 HALL sensing characteristics

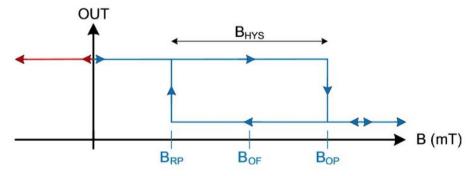

Figure 4.1: Magnet trigger level description (active low output)

| Table 4-6: | Example | power-on | magnet | detection | options. |

|------------|---------|----------|--------|-----------|----------|

|------------|---------|----------|--------|-----------|----------|

| HALL sensor setup    | Output<br>type  | B <sub>RP</sub><br>(mT)                                | B <sub>OP</sub><br>(mT) <sup>1</sup> | В <sub>нуs</sub><br>(mT)                         | B <sub>RP</sub> and B <sub>OP</sub><br>accuracy (mT)<br>-20°C to 60°C <sup>2</sup> |

|----------------------|-----------------|--------------------------------------------------------|--------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------|

| Threshold Example 1  | Direct          | 9.5                                                    | 10                                   | 0.5                                              | ± 4                                                                                |

| Threshold Example 3  | Direct          | 42.5                                                   | 45                                   | 2.5                                              | ± 18                                                                               |

| Adjustable Threshold | I2C /<br>Direct | 25 –<br>100% of<br>B <sub>OP</sub><br>(default<br>95%) | Software<br>register                 | 0 – 75%<br>of B <sub>OP</sub><br>(default<br>5%) | ± 40%                                                                              |

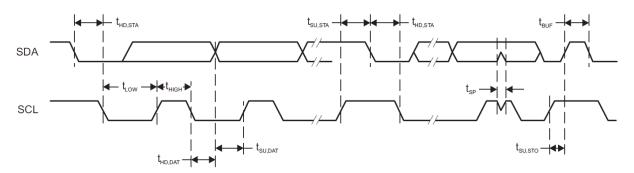

## 4.4.4 I<sup>2</sup>C

Specified over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| Parameter           |                                                     | Test conditions            |            | Min               | Тур       | Max   | Unit |  |

|---------------------|-----------------------------------------------------|----------------------------|------------|-------------------|-----------|-------|------|--|

| f <sub>SYS</sub>    | System clock frequency                              |                            |            | 15.68             | 16.00     | 16.32 | MHz  |  |

| f <sub>SCL</sub>    | SCL clock frequency                                 |                            | 1.8 V, 3 V | 0                 |           | 400   | kHz  |  |

| t <sub>HD,STA</sub> | Hold time (repeated) START                          | f <sub>scL</sub> = 100 kHz | 1.8 V, 3 V | 4.0               |           |       | μs   |  |

|                     |                                                     | f <sub>SCL</sub> > 100 kHz |            | 0.6               |           |       |      |  |

| t <sub>su,sta</sub> | Setup time for a repeated START                     | f <sub>scL</sub> = 100 kHz | 1.8 V, 3 V | 4.7               |           |       | μs   |  |

|                     |                                                     | f <sub>SCL</sub> > 100 kHz |            | 0.6               |           |       |      |  |

| t <sub>HD,DAT</sub> | Data hold time                                      |                            | 1.8 V, 3 V | 0                 |           |       | ns   |  |

| t <sub>SU,DAT</sub> | Data setup time                                     |                            | 1.8 V, 3 V | 250               |           |       | ns   |  |

| t <sub>SU,STO</sub> | Setup time for STOP                                 | f <sub>scL</sub> = 100 kHz | 1.8 V, 3 V | 4.0               |           |       | μs   |  |

|                     |                                                     | f <sub>SCL</sub> > 100 kHz |            | 0.6               |           |       | 1    |  |

| t <sub>SP</sub>     | Pulse duration of spikes suppressed by input filter | N/A                        | 1.8 V, 3 V | No puls<br>filter | se suppre | ssion | ns   |  |

| t <sub>LOW</sub>    | Clock low time-out                                  | N/A                        | 1.8 V, 3 V | TBD               |           |       | ms   |  |

<sup>&</sup>lt;sup>1</sup> Preliminary values based on expected single and dual magnet applications. These values are flexible and different ordering options will exist. Typical trigger level at 25degC

<sup>&</sup>lt;sup>2</sup> Applicable when no temperature compensation is used. When using temperature compensation, accuracy is drastically improved.

### 4.5 **Current consumption**

### 4.5.1 **Reset User Interfaces**

*Table 4-7* lists current consumption during RUI operation with no communication. Rui power mode is Normal Power Mode with a Report Rate of 150ms and a Ready Timeout of 30ms. Since the full Ready Timeout time can lapse, the total time for each report cycle is 180ms. For the open drain "Ready Type" measurements, a  $4.7 k\Omega$  pull-up resistor was used.

| Magnetic   | Supply Voltage | Ready Type  | RUI  | Averaged Current (µA) |        |      |  |

|------------|----------------|-------------|------|-----------------------|--------|------|--|

| Field (mT) | (V)            |             | KUI  | Min.                  | Тур.   | Max. |  |

|            |                |             | RUI1 | -                     | 80.89  | -    |  |

|            |                | Open Drain, | RUI2 | -                     | 74.91  | -    |  |

|            |                | Active Low  | RUI3 | -                     | TBD    | -    |  |

|            | 1.0            |             | RUI4 | -                     | TBD    | -    |  |

|            | 1.8            |             | RUI1 | -                     | 12.98  | -    |  |

|            |                | Push Pull,  | RUI2 | -                     | 6.13   | -    |  |

|            |                | Active High | RUI3 | -                     | TBD    | -    |  |

| 0          |                |             | RUI4 | -                     | TBD    | -    |  |

|            |                |             | RUI1 | -                     | 138.21 | -    |  |

| 3.3        |                | Open Drain, | RUI2 | -                     | 132.04 | -    |  |

|            |                | Active Low  | RUI3 | -                     | TBD    | -    |  |

|            | 3.3            |             | RUI4 | -                     | TBD    | -    |  |

|            |                | RUI1        | -    | 23.65                 | -      |      |  |

|            | Push Pull,     | RUI2        | -    | 15.32                 | -      |      |  |

|            |                | Active High | RUI3 | -                     | TBD    | -    |  |

|            |                |             | RUI4 | -                     | TBD    | -    |  |

|            |                |             | RUI1 | -                     | 84.41  | -    |  |

|            |                | Open Drain, | RUI2 | -                     | 74.91  | -    |  |

|            |                | Active Low  | RUI3 | -                     | TBD    | -    |  |

|            | 1.8            |             | RUI4 | -                     | TBD    | -    |  |

|            |                |             | RUI1 | -                     | 15.53  | -    |  |

|            |                | Push Pull,  | RUI2 | -                     | 6.13   | -    |  |

|            |                | Active High | RUI3 | -                     | TBD    | -    |  |

| 18         |                |             | RUI4 | -                     | TBD    | -    |  |

|            |                |             | RUI1 | -                     | 139.07 | -    |  |

|            |                | Open Drain, | RUI2 | -                     | 132.04 | -    |  |

|            |                | Active Low  | RUI3 | -                     | TBD    | -    |  |

|            | 2.2            |             | RUI4 | -                     | TBD    | -    |  |

|            | 3.3            |             | RUI1 | -                     | 20.08  | -    |  |

|            |                | Push Pull,  | RUI2 | -                     | 15.32  | -    |  |

|            |                | Active High | RUI3 | -                     | TBD    | -    |  |

|            |                |             | RUI4 | -                     | TBD    | -    |  |

Table 4-7: Current consumption during RUI operation before any communication.

*Table 4-8* lists current consumption measurements after reset has been acknowledged and Event Mode has been enabled. The IQS626A device is then placed into the required Power Mode and current is measured. No other settings are altered. Since the ready pin is not toggled during this measurement, the Ready Type settings is not listed.

|                        |                          |      |      |                     | Avera | ged Cur | rent Con            | sumptio | n (uA) |                               |      |

|------------------------|--------------------------|------|------|---------------------|-------|---------|---------------------|---------|--------|-------------------------------|------|

| Magnetic<br>Field (mT) | Supply<br>Voltage<br>(V) | RUI  |      | al Power<br>s Repor |       |         | Power M<br>s Report |         |        | a-Low Po<br>(256ms  <br>Rate) |      |

|                        |                          |      | Min. | Тур.                | Max.  | Min.    | Тур.                | Max.    | Min.   | Тур.                          | Max. |

|                        |                          | RUI1 | -    | 14.32               | -     | -       | 14.32               | -       | -      | 3.08                          | -    |

|                        | 1.8                      | RUI2 | -    | 8.48                | -     | -       | 8.48                | -       | -      | 2.96                          | -    |

|                        | 1.0                      | RUI3 | -    | TBD                 | -     | -       | TBD                 | -       | -      | TBD                           | -    |

| 0                      |                          | RUI4 | -    | TBD                 | -     | -       | TBD                 | -       | -      | TBD                           | -    |

|                        |                          | RUI1 | -    | 14.91               | -     | -       | 14.91               | -       | -      | 3.61                          | -    |

|                        | 3.3                      | RUI2 | -    | 9.15                | -     | -       | 9.15                | -       | -      | 3.61                          | -    |

|                        |                          | RUI3 | -    | TBD                 | -     | -       | TBD                 | -       | -      | TBD                           | -    |

|                        |                          | RUI4 | -    | TBD                 | -     | -       | TBD                 | -       | -      | TBD                           | -    |

|                        |                          | RUI1 | -    | 14.02               | -     | -       | 14.02               | -       | -      | 3.06                          | -    |

|                        | 1.8                      | RUI2 | -    | 8.48                | -     | -       | 8.48                | -       | -      | 2.96                          | -    |

|                        | 1.0                      | RUI3 | -    | TBD                 | -     | -       | TBD                 | -       | -      | TBD                           | -    |

| 18                     |                          | RUI4 | -    | TBD                 | -     | -       | TBD                 | -       | -      | TBD                           | -    |

|                        |                          | RUI1 | -    | 14.48               | -     | -       | 14.84               | -       | -      | 3.72                          | -    |

|                        | 3.3                      | RUI2 | -    | 9.15                | -     | -       | 9.15                | -       | -      | 3.61                          | -    |

|                        |                          | RUI3 | -    | TBD                 | -     | -       | TBD                 | -       | -      | TBD                           | -    |

|                        |                          | RUI4 | -    | TBD                 | -     | -       | TBD                 | -       | -      | TBD                           | -    |

#### Table 4-8: Current consumption during with default RUI settings and Event Mode enabled.

## 5 Identification

## 5.1 Revision Identification

The device revision information is included as part of the top-side marking on the device package as shown below. The hardware revision is also stored as shown in the table below:

| Description                                                                                | Address | Offset 0                                   | Offset 1                                   |

|--------------------------------------------------------------------------------------------|---------|--------------------------------------------|--------------------------------------------|

| Product number (1 <sup>st</sup> byte), Version number (2 <sup>nd</sup> byte)               | 00h     | 0x51                                       | 0x01 (pre-production)<br>0x02 (production) |

| Hardware revision (1 <sup>st</sup> byte), Reserved development code (2 <sup>nd</sup> byte) | 01h     | 0x0A (pre-production)<br>0x2D (production) | Reserved                                   |

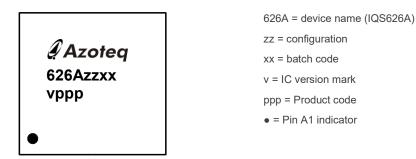

## 5.2 WLCSP-16 Device Identification

The device type can be identified from the top-side marking on the device package as shown below:

|   |      | 626A = device name (IQS626A)                     |

|---|------|--------------------------------------------------|

|   | 626A | zz = configuration / xx = batch code (AA, AB ZZ) |

|   | ZZXX | v = IC version mark                              |

|   | vppp | ppp = product code                               |

| l | •    | • = Pin A1 indicator                             |

### 5.3 **QFN16 Device Identification**

The device type can be identified from the top-side marking on the device package as shown below:

A device identification value is also stored as shown in the table above.

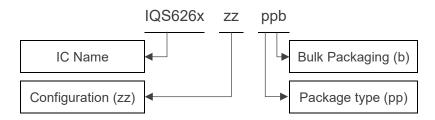

## 6 Ordering information

Please check stock availability with your local distributor.

| IC NAME        | IQS626x | = | IQS626A                                                           |

|----------------|---------|---|-------------------------------------------------------------------|

|                |         |   |                                                                   |

| CONFIGURATION  | ZZ      | = | IC configuration (hexadecimal)                                    |

|                |         | = | <b>00</b> (default)<br><b>zz</b> (Minimum order quantities apply) |

| PACKAGE TYPE   | рр      | = | QN: QFN-16 package (special order)                                |

|                | рр      | = | CS: WLCSP-16 package                                              |

| BULK PACKAGING | b       | = | R: Reel (3000pcs/reel) – MOQ = 3000pcs                            |

|                |         | = | MOQ = 1 reel (orders shipped as full reels)                       |

## 7 Package specification

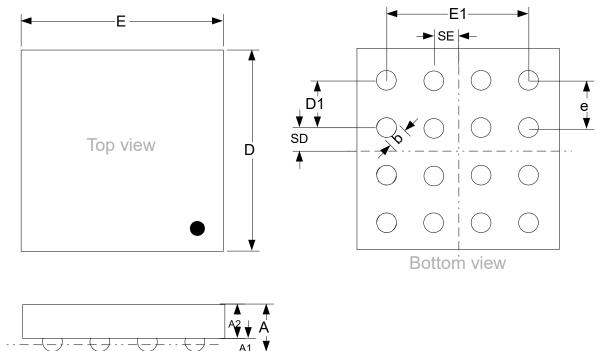

## 7.1 Package outline description – WLCSP-16

Side view

| Dimension | [mm]       | Dimension | [mm]      |

|-----------|------------|-----------|-----------|

| A         | 0.5±0.05   | D1        | 0.4±0.025 |

| A1        | 0.2±0.015  | SD        | 0.2 BSC   |

| A2        | 0.3±0.025  | E         | 1.62±0.05 |

| b         | 0.25±0.025 | E1        | 1.2       |

| D         | 1.62±0.05  | SE        | 0.2 BSC   |

|           |            | е         | 0.4 BSC   |

Figure 7.1: WLCSP(1.62x1.62)–16 Package

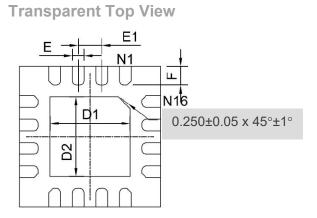

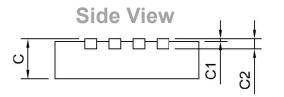

## 7.2 Package outline description – QFN-16

| Dimension | [mm]        | Dimension | [mm]      |

|-----------|-------------|-----------|-----------|

| А         | 3.0±0.1     | D1        | 1.7±0.05  |

| В         | 3.0±0.1     | D2        | 1.7±0.05  |

| С         | 0.75±0.05   | E         | 0.25±0.05 |

| C1        | 0.025±0.025 | E1        | 0.5±0.05  |

| C2        | 0.203±0.05  | F         | 0.4±0.05  |

Figure 7.2: QFN(3x3)–16 Package

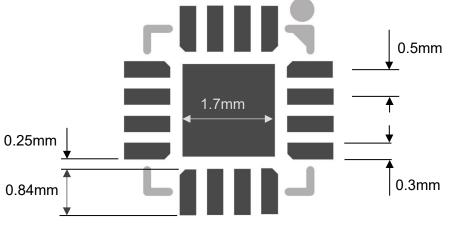

## 7.3 **QFN16 recommended PCB/FPC footprint**

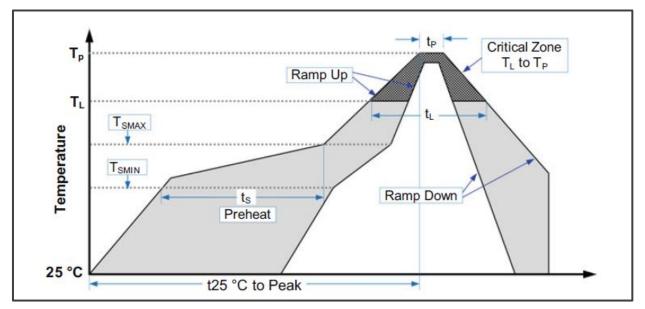

## 7.4 Reflow specification

#### Table 7-1: WLCSP-16 reflow specifications

| Azoteq reflo                                       | w solder profile                       |

|----------------------------------------------------|----------------------------------------|

| Device                                             | IQS626A                                |

| Package                                            | WLCSP-16 (1.62 x 1.62 x 0.4mm)         |

| Compatibility                                      | Industry standard reflow for Lead-free |

| Reflow count                                       | Up to 4 times (J-STD-020)              |

| ofile feature                                      | Value                                  |

| verage ramp rate ( $T_L$ to $T_P$ )                | 1-3°C/s                                |

| reheat                                             |                                        |

| Minimum temperature (T <sub>SMIN</sub> )           | 130°C                                  |

| Maximum temperature (T <sub>SMAX</sub> )           | 200°C                                  |

| Soak time ( $T_{SMIN}$ to $T_{SMAX}$ ) ts          | 60 - 75s                               |

| amp-up rate (T <sub>SMAX</sub> to TL)              | 1.25°C                                 |

| me above liquidus (t∟)                             | 60 - 150s                              |

| quidous temperature (T∟)                           | 217°C                                  |

| eak temperature (T <sub>P</sub> )                  | 255 - 260°C                            |

| me within 5°C of actual peak temperature ( $t_P$ ) | 20 - 30s                               |

| amp down rate                                      | 3°C/s max                              |

| me from 25°C of peak temperature                   | 480s max                               |

Figure 7.4: WLCSP-16 reflow solder profile

## 8 Register Map

The IQS626A contains mostly volatile memory which must be configured via the *I2C Interface* after reset in order to achieve the desired device functionality. Herewith follows the complete register map of the IQS626A. For a detailed description of each register, see the *Detailed Register Descriptions* in appendix A.

Some bits in Read-Write registers are marked as Reserved(*val*), such bits must be kept at the value specified by *val*, the key for *val* is as follows:

- > 0 –Write to 0

- > 1 Write to 1

- > X Don't Care

- Z Do not change

## 8.1 System Information Registers

#### Table 8-1: System Information Registers

| Full<br>Address | Group Name                            | Item Nar                | ne (offse                    | t 0: bit 7–                   | bit 0)          |       |                               |                 |                          | ltem Nan            | ne (offset              | 1: bit 7–                     | bit 0)         |                          |               |           |        | Data<br>Access                 |

|-----------------|---------------------------------------|-------------------------|------------------------------|-------------------------------|-----------------|-------|-------------------------------|-----------------|--------------------------|---------------------|-------------------------|-------------------------------|----------------|--------------------------|---------------|-----------|--------|--------------------------------|

|                 |                                       | Bit 7                   |                              |                               |                 |       |                               |                 | Bit 0                    | Bit 7               |                         |                               |                |                          |               |           | Bit 0  |                                |

| 0x00            | Version Info                          |                         | Number<br>QS626A             |                               |                 |       |                               |                 |                          |                     |                         | tion firmw                    | are            |                          |               |           |        | Read-<br>Only                  |

| 0x01            |                                       | Hardwar<br>Reserve      | r <u>e Numbe</u><br>d        | r                             |                 |       |                               |                 |                          | Reserved            | d                       | to read or                    |                | ccessible<br>byte will a | ccess the     | following | byte.  | Read-<br>Only                  |

| 0x02            | <u>Global Flags</u>                   | System<br>Show<br>Reset | Flags<br>Reserve             | ed                            | ATI in progress | EVENT | ULP<br>updating<br>all active | reg 0x80        | node (see<br>) bits 5:4) | POWER               | vent Flag<br>SYSTE<br>M | REFER                         | RESER<br>VED   | GESTU<br>RE              | DEEP<br>TOUCH | TOUCH     | PROX   | Read-<br>Only                  |

| 0x03            | Gesture Event                         | Gesture                 | Event Fla                    | ags (Track                    | (nad)           |       | channel<br>s                  |                 |                          | E                   | 4                       | EL                            |                |                          |               |           |        | Read-                          |

|                 | <u>Flags</u>                          |                         |                              | HOLD                          | TAP             |       | POS_Y_<br>FLICK               | NEG_X<br>_FLICK |                          | An                  | y attempt               | to read or                    | write this     | ccessible<br>byte will a | access the    | following | byte.  | Only                           |

| 0x04            | Channel States                        |                         | CH2                          | Generic<br>CH1                | Generic<br>CH0  |       |                               |                 | ULP CH                   |                     | Generic<br>CH2          | y Directior<br>Generic<br>CH1 | Generic<br>CH0 |                          |               |           | ULP CH | ,                              |

| 0x05            |                                       |                         | Is Touch S<br>Generic<br>CH2 | State<br>Generic<br>CH1       | Generic<br>CH0  |       |                               | TP              | ULP CH                   | Channel             |                         | Generic<br>CH1                |                |                          |               |           |        | Read-<br>Only                  |

| 0x06            |                                       | Referen                 | ce channe                    | els activel<br>Generic<br>CH1 | y used          |       |                               | [               |                          | Reserve             | d                       | to read or                    | Not Ad         | ccessible<br>byte will a | ccess the     | followina | bvte.  | Read-<br>Only                  |

| 0x07            |                                       |                         |                              | Generic<br>CH1                |                 |       |                               | TP              | ULP CH                   | Channel             | compens                 | ation maxi<br>Generic<br>CH1  | mum flag       |                          |               | TP        | ULP CH | Read-<br>Only                  |

| 0x08            | <u>Trackpad</u><br><u>Coordinates</u> | X Coord                 | inate                        | •                             |                 |       |                               |                 |                          | Y Coordi<br>0 – 255 |                         | 1                             |                |                          |               |           |        | Read-<br>Only                  |

| 0x09            | Counts & LTA                          |                         |                              | (pad); 0 –<br>ITS ULTR        |                 |       |                               |                 |                          | 0 - 200             |                         |                               |                |                          |               |           |        | Read-<br>Only                  |

| 0x0A<br>0x0B    |                                       |                         |                              | ERAGE UI                      | -               |       | -                             | IEL             |                          |                     |                         |                               |                |                          |               |           |        | Read-<br>Only<br>Read-         |

| 0x0B            | -                                     |                         |                              | ERAGE TH                      |                 |       |                               |                 |                          |                     |                         |                               |                |                          |               |           |        | Only<br>Read-                  |

| 0x0D            | -                                     | FILTER                  | ED COUN                      | ITS TRAC                      | KPAD CH         | ANNEL | 1                             |                 |                          |                     |                         |                               |                |                          |               |           |        | Only<br>Read-<br>Only          |

| 0x0E            |                                       |                         |                              | ERAGE TH                      | -               | -     |                               |                 |                          |                     |                         |                               |                |                          |               |           |        | Read-<br>Only                  |

| 0x0F<br>0x10    | -                                     |                         |                              | ITS TRAC                      |                 |       |                               |                 |                          |                     |                         |                               |                |                          |               |           |        | Read-<br>Only<br>Read-         |

| 0x10            | -                                     |                         |                              |                               |                 |       |                               |                 |                          |                     |                         |                               |                |                          |               |           |        | Only<br>Read-                  |

| 0x12            |                                       | LONG T                  | ERM AVE                      | ERAGE TH                      | RACKPAE         | CHANN | IEL 3                         |                 |                          |                     |                         |                               |                |                          |               |           |        | Only<br>Read-<br>Only          |

| 0x13            | ]                                     |                         |                              | ITS TRAC                      | -               |       |                               |                 |                          |                     |                         |                               |                |                          |               |           |        | Read-<br>Only                  |

| 0x14<br>0x15    | -                                     |                         |                              | ERAGE TH                      |                 | -     |                               |                 |                          |                     |                         |                               |                |                          |               |           |        | Read-<br>Only<br>Read-         |

| 0x15<br>0x16    | -                                     |                         |                              | ERAGE TH                      |                 |       |                               |                 |                          |                     |                         |                               |                |                          |               |           |        | Read-<br>Only<br>Read-<br>Only |

| Full<br>Address | Group Name     | Item Name (off | set 0: bit 7- | · bit 0) |           |         |         |       | Item Na | me (offs | et 1: bit | 7– bit 0) |  |       | Data<br>Access |

|-----------------|----------------|----------------|---------------|----------|-----------|---------|---------|-------|---------|----------|-----------|-----------|--|-------|----------------|

|                 |                | Bit 7          |               |          |           |         |         | Bit 0 | Bit 7   |          |           |           |  | Bit 0 |                |

| 0x17            |                | FILTERED COU   | JNTS TRAC     | KPAD CH  | ANNEL 6   | ;<br>;  |         |       |         |          |           |           |  |       | Read-          |

|                 |                |                |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x18            |                | LONG TERM A    | VERAGE TF     | RACKPAD  | CHANNE    | EL 6    |         |       |         |          |           |           |  |       | Read-          |

|                 |                |                |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x19            |                | FILTERED COU   | JNTS TRAC     | KPAD CH  | ANNEL 7   | ,       |         |       |         |          |           |           |  |       | Read-          |

| 01.4            |                | LONG TERM A    |               |          |           | -1 -7   |         |       |         |          |           |           |  |       | Only           |

| 0x1A            |                | LONG TERM A    | VERAGE IF     | KACKPAL  | CHANNE    | EL /    |         |       |         |          |           |           |  |       | Read-<br>Onlv  |

| 0x1B            |                | FILTERED COL   | INTS TRAC     |          |           | 1       |         |       |         |          |           |           |  |       | Read-          |

| UXID            |                |                |               |          |           | ,       |         |       |         |          |           |           |  |       | Only           |

| 0x1C            |                | LONG TERM A    | VERAGE TF     | RACKPAD  | CHANNE    | EL 8    |         |       |         |          |           |           |  |       | Read-          |

|                 |                |                |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x1D            |                | FILTERED COU   | JNTS GENE     | RIC CHA  | NNEL 0    |         |         |       |         |          |           |           |  |       | Read-          |

|                 |                |                |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x1E            |                | LONG TERM A    | VERAGE GE     | ENERIC C | CHANNEL   | . 0     |         |       |         |          |           |           |  |       | Read-          |

|                 |                |                |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x1F            |                | FILTERED COU   | JNTS GENE     | RIC CHA  | NNEL 1    |         |         |       |         |          |           |           |  |       | Read-          |

| 0x20            |                | LONG TERM A    |               |          |           | 4       |         |       |         |          |           |           |  |       | Only<br>Read-  |

| 0.120           |                | LONG TERM A    | VERAGE GI     |          |           | . '     |         |       |         |          |           |           |  |       | Only           |

| 0x21            |                | FILTERED COL   | INTS GENE     | RIC CHA  | NNFI 2    |         |         |       |         |          |           |           |  |       | Read-          |

| 0/121           |                |                |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x22            |                | LONG TERM A    | VERAGE GE     | ENERIC C | CHANNEL   | . 2     |         |       |         |          |           |           |  |       | Read-          |

|                 |                |                |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x23            | Hall-Effect    | HALL OUTPUT    |               |          |           |         |         |       |         |          |           |           |  |       | Read-          |

|                 | Channel        |                |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x24            | <u>Outputs</u> | HALL COMMO     | N             |          |           |         |         |       |         |          |           |           |  |       | Read-          |

| 0x25            |                | FILTERED COL   |               |          |           |         |         |       |         |          |           |           |  |       | Only<br>Read-  |

| UX25            |                | FILTERED COU   | JN15 HALL     | PLATE    |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x26            |                | FILTERED COL   | INTS HALL     | PLATE 1  |           |         |         |       |         |          |           |           |  |       | Read-          |

| 0/120           |                |                |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x27            | Reference      | REFERENCE C    | HANNEL D      | ELTA FO  | R ULP CH  | IANNEL  |         |       |         |          |           |           |  |       | Read-          |

|                 | Channel Deltas |                |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x28            |                | REFERENCE C    | HANNEL D      | ELTA FOI | R TRACK   | PAD CHA | ANNELS  |       |         |          |           |           |  |       | Read-          |

|                 |                |                |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x29            |                | REFERENCE C    | HANNEL D      | ELTA FOI | R GENER   | AL CHAN | NNEL 0  |       |         |          |           |           |  |       | Read-          |

| 0               |                | REFERENCE C    |               |          |           |         |         |       |         |          |           |           |  |       | Only           |

| 0x2A            |                | REFERENCE      |               | ELIAFO   | R GENER   |         | NINEL 1 |       |         |          |           |           |  |       | Read-<br>Onlv  |

| 0x2B            |                | REFERENCE C    |               |          |           |         | NNEL 2  |       |         |          |           |           |  |       | Read-          |

| 0720            |                |                |               |          | N OLINEIN |         |         |       |         |          |           |           |  |       | Only           |

## 8.2 General Settings Registers

### Table 8-2: General Settings Registers

| Full<br>Address | Group Name             | Item Nar                                                         | ne (offse                                                                                                              | t 0: bit 7-                                                               | • bit 0)                                                                                                      |                                                                |                                                                                                                  |                                                                                      |                                       | Item Nar                | ne (offse                  | t 1: bit 7–                                    | bit 0)                     |                            |                                                                                   |              |                                                                               | Data<br>Access |

|-----------------|------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------|-------------------------|----------------------------|------------------------------------------------|----------------------------|----------------------------|-----------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------|----------------|

|                 |                        | Bit 7                                                            |                                                                                                                        |                                                                           |                                                                                                               |                                                                |                                                                                                                  |                                                                                      | Bit 0                                 | Bit 7                   |                            |                                                |                            |                            |                                                                                   |              | Bit 0                                                                         |                |

|                 | Power Mode             | Power M                                                          |                                                                                                                        |                                                                           |                                                                                                               |                                                                | -                                                                                                                |                                                                                      |                                       | I <sup>2</sup> C settin |                            | -                                              |                            | -                          |                                                                                   | -            |                                                                               | Read-          |

| 0x80            | and System<br>Settings | Main<br>oscillator<br>change<br>'0' –<br>16MHz,<br>'1' –<br>4MHz | CH0<br>ultra low<br>power                                                                                              | Auto<br>Power<br>Mode<br>Switchin<br>g<br>'0'<br>enable<br>'1'<br>disable | Power m<br>selection<br>auto mod<br>switching<br>disabled<br>'00' – NF<br>'01' – LP<br>'10' – UL<br>'11' – Ha | n (when<br>de<br>g is<br>)<br>                                 | NP Segn<br>in ULP m<br>during Ul<br>'000' – 8,<br>'010' – 24<br>'100' – 89<br>'110' – 19                         | iode (mai<br>ate of all o<br>LP mode<br>('001' – 1<br>3, '011' –<br>9, '101' –       | nage<br>channels<br>3,<br>54,<br>135, | Reserve<br>d (0)        | Advan-<br>ced <sup>1</sup> | Event<br>mode '0'<br>Disable,<br>'1'<br>Enable | Advan-<br>ced <sup>2</sup> | Advan-<br>ced <sup>3</sup> | CMD:<br>REDO-<br>ATI<br>(Define<br>channels<br>to ATI in<br>reg 0x88<br>offset 1) |              | CMD:<br>ACK-<br>RESET<br>(Clears<br>"Show<br>reset" –<br>reg 0x02<br>offset 0 | Write          |