IQS316 Design Guide IQ Switch<sup>®</sup> - ProxSense<sup>®</sup> Series

Multi-channel Integrated Proximity Sensor with Micro-Processor Core

This design guide provides a description of the communication interface between the master and the IQS316 controller. The Memory Map of the IQS316 is provided in this document, followed by a description of each register and instruction. The IQS316 communicates in I<sup>2</sup>C or SPI mode, both using a Memory Mapped structure. The last section of this document is dedicated to an example implementation and provides example code.

# Contents

| IC | <b>\\$316 De</b> | sign Guide                                 |    |

|----|------------------|--------------------------------------------|----|

| 1  | Mem              | ory Map                                    |    |

|    | 1.1              | General Memory Map Structure               | 4  |

|    | 1.2              | IQS316 Memory Map                          |    |

|    | 1.2.1            | Device Information                         |    |

|    | 1.2.2            | Device Specific Data                       |    |

|    | 1.2.3            | Proximity Status Bytes                     | 6  |

|    | 1.2.4            | Touch Status Bytes                         | 6  |

|    | 1.2.5            | Halt Bytes                                 | 7  |

|    | 1.2.6            | Active Bytes                               | 7  |

|    | 1.2.7            | Current Samples                            |    |

|    | 1.2.8            | Long-Term Averages and Thresholds          |    |

|    | 1.2.9            | Device Settings                            |    |

|    | 1.3              | Memory Map Description                     |    |

|    | 1.3.1            | Device Information                         |    |

|    | 1.3.2            | Device Specific Data                       |    |

|    | 1.3.3            | Proximity Status Bytes                     |    |

|    | 1.3.4            | Touch Status Bytes                         |    |

|    | 1.3.5            | Halt Bytes                                 |    |

|    | 1.3.6            | Active Bytes                               |    |

|    | 1.3.7            | Current Samples                            |    |

|    | 1.3.8            | Long-Term Averages & Touch/Prox Thresholds |    |

|    | 1.3.9            | Device Settings                            |    |

| 2  | Gene             | ral Implementation hints                   | 29 |

|    | 2.1              | Communication window                       |    |

|    | 2.1.1            | SPI Communication window                   |    |

|    | 2.1.2            | I <sup>2</sup> C Communication window      |    |

|    | 2.2              | Startup Procedure                          |    |

|    | 2.2.1            | Individual Prox and Touch Thresholds       |    |

|    | 2.2.2            | Auto ATI Procedure                         |    |

|    | 2.2.3            | Post Setup                                 |    |

|    | 2.3              | General I <sup>2</sup> C Hints             |    |

|    | 2.3.1            | I <sup>2</sup> C Pull-up resistors         |    |

|    | 2.3.2            | MCLR                                       |    |

|    | 2.3.3            | Reset Device while using I <sup>2</sup> C  |    |

| 3  | Samp             | le implementation                          | 31 |

|    | 3.1              | Overview                                   |    |

|    | 3.1.1            |                                            |    |

|    | 3.2              | Functions                                  |    |

|    | 3.2.1            | IQS316_Settings                            |    |

|    | 3.2.2            | IQS316_Refresh_Data                        |    |

|    | 3.2.3            | IQS316_Process_Data                        |    |

|    | 3.2.4            | Main Function (I <sup>2</sup> C and SPI)   |    |

|    | 3.2.5            | Comms_init                                 |    |

|    | 3.2.6            | IQS316_Read                                |    |

|    | 3.2.7            | IQS316_ReadCurrentAddress                  |    |

| 3.2.8  | IQS316 Write                | 44 |

|--------|-----------------------------|----|

|        | IQS316_End_Comms_Window     |    |

| 3.2.10 | Comms_Error                 | 46 |

| 3.2.11 | l <sup>2</sup> C byte write | 46 |

| 3.2.12 | Read with NACK              | 47 |

| 3.2.13 | Read with ACK               | 47 |

| 3.2.14 | I <sup>2</sup> C START      | 48 |

| 3.2.15 | I <sup>2</sup> C STOP       | 48 |

| 3.2.16 | SPI Receive/Transmit        | 48 |

| 3.2.17 | Constant Declarations       | 49 |

|        |                             |    |

# 1 Memory Map

# 1.1 General Memory Map Structure

A general I<sup>2</sup>C and SPI Memory Map is defined so that all ProxSense<sup>®</sup> devices can use a standard framework. The general mapping is shown below.

| Address | Access | Size(Bytes) | Device Information |

|---------|--------|-------------|--------------------|

| 00H-0FH | R      | 16          | Device mornation   |

| Table 1.1 | <b>IQS316</b> | Memory | Mapping |

|-----------|---------------|--------|---------|

|-----------|---------------|--------|---------|

| Address | Access | Size(Bytes) | Device Specific Data |

|---------|--------|-------------|----------------------|

| 10H-30H | R      | 32          | Device Specific Data |

| Prov          |

|---------------|

| <u>Proxii</u> |

| Address     | Access | Size(Bytes) |            |

|-------------|--------|-------------|------------|

| 39H-<br>3CH | R      | 4           | Halt Bytes |

| Address     | Access | Size(Bytes) |

|-------------|--------|-------------|

| 3DH-<br>41H | R      | 4           |

| Address | Access | Size(Bytes) | Current Samples |

|---------|--------|-------------|-----------------|

| 42H-82H | R      | 64          | Current Samples |

| Address     | Access | Size(Bytes) |             |

|-------------|--------|-------------|-------------|

| 83H-<br>C3H | R/W    | 64          | <u>LTAs</u> |

| Address     | Access | Size(Bytes) |                 |

|-------------|--------|-------------|-----------------|

| C4h-<br>FDh | R/W    | 64          | Device Settings |

\* Note 'FE' and 'FF' are reserved for other functions in communication.

# 1.2 IQS316 Memory Map

# 1.2.1 **Device Information**

| Address |       |   | Product Number |   |        |         |   |   |   |  |  |  |

|---------|-------|---|----------------|---|--------|---------|---|---|---|--|--|--|

| 00H     | Bit   | 7 | 6              | 5 | 4      | 3       | 2 | 1 | 0 |  |  |  |

| Access  | Value |   |                |   | 27 (De | ecimal) |   |   |   |  |  |  |

| R       |       |   |                |   |        |         |   |   |   |  |  |  |

| Address |       |   | Version Number |   |      |      |   |   |   |  |  |  |

|---------|-------|---|----------------|---|------|------|---|---|---|--|--|--|

| 01H     | Bit   | 7 | 6              | 5 | 4    | 3    | 2 | 1 | 0 |  |  |  |

| Access  | Value |   |                |   | Vari | able |   |   |   |  |  |  |

| R       |       |   |                |   |      |      |   |   |   |  |  |  |

## 1.2.2 Device Specific Data

| Address |       |            | <u>XY Inf</u>  | <u>o 1</u> | <u>(UI</u> | FL | <u>.AGS0)</u> |             |       |

|---------|-------|------------|----------------|------------|------------|----|---------------|-------------|-------|

| 10H     | Bit   | 7          | 6              | 5          | 4          | 3  | 2             | 1           | 0     |

| Access  | Value | SHOW_RESET | MODE_INDICATOR | ~          | 2          | ~  | ATI_BUSY      | RESEED_BUSY | NOISE |

| R       |       |            |                |            |            |    |               |             |       |

### 1.2.3 Proximity Status Bytes

Only the proximity status of the channels relating to the current group is available here.

| Address |      |              |        |        | <u>Prox</u> | imity Status | (Group dep | endant) |      |

|---------|------|--------------|--------|--------|-------------|--------------|------------|---------|------|

| 31H     | Bit  | 7 6 5 4      |        |        |             | 3            | 2          | 1       | 0    |

| Access  | Name | If Group = 0 |        |        |             | CH3          | CH2        | CH1     | CH0  |

| R       | Name |              | lf Gro | up = 1 |             | CH7          | CH6        | CH5     | CH4  |

|         | Name |              | lf Gro | up = 2 | 2           | CH11         | CH10       | CH9     | CH8  |

|         | Name | If Group = 3 |        |        |             | CH15         | CH14       | CH13    | CH12 |

|         | Name | If Group = 4 |        |        | ŀ           | CH19         | CH18       | CH17    | CH16 |

# 1.2.4 Touch Status Bytes

Only the touch status of the channels relating to the current group is available here.

| Address |      |              |        |        | <u>Τοι</u> | uch Status ( | Group deper | ndant) |      |

|---------|------|--------------|--------|--------|------------|--------------|-------------|--------|------|

| 35H     | Bit  | 7            | 6      | 5      | 4          | 3            | 2           | 1      | 0    |

| Access  | Name |              | lf Gro | up = C | )          | 7            | ~           | ~      | ~    |

| R       | Name |              | lf Gro | up = 1 |            | CH7          | CH6         | CH5    | CH4  |

|         | Name |              | lf Gro | up = 2 | 2          | CH11         | CH10        | CH9    | CH8  |

|         | Name | If Group = 3 |        |        |            | CH15         | CH14        | CH13   | CH12 |

|         | Name | If Group = 4 |        |        |            | CH19         | CH18        | CH17   | CH16 |

\*Note: This byte is not used for Group 0 (Prox Mode)

## 1.2.5 Halt Bytes

Only the filter halt status of the channels relating to the current group is available here.

| Address |      |              |        |        | Ha | alt Status (G | roup depend | dant) |      |

|---------|------|--------------|--------|--------|----|---------------|-------------|-------|------|

| 39H     | Bit  | 7            | 6      | 5      | 4  | 3             | 2           | 1     | 0    |

| Access  | Name | If Group = 0 |        |        |    | CH3           | CH2         | CH1   | CH0  |

| R       | Name |              | lf Gro | up = 1 | 1  | CH7           | CH6         | CH5   | CH4  |

|         | Name |              | lf Gro | up = 2 | 2  | CH11          | CH10        | CH9   | CH8  |

|         | Name | If Group = 3 |        |        |    | CH15          | CH14        | CH13  | CH12 |

|         | Name | If Group = 4 |        |        |    | CH19          | CH18        | CH17  | CH16 |

### 1.2.6 Active Bytes

The group number is given here.

| Address |       |   | Group Number |         |           |            |            |          |   |  |  |

|---------|-------|---|--------------|---------|-----------|------------|------------|----------|---|--|--|

| 3DH     | Bit   | 7 | 6            | 5       | 4         | 3          | 2          | 1        | 0 |  |  |

| Access  | Value |   |              |         | Variabl   | e (0-4)    |            |          |   |  |  |

| R       | Note  |   | Indicate     | s which | group's c | lata is cu | irrently a | vailable |   |  |  |

## 1.2.7 Current Samples

The Current Samples of the current group are available here.

| Address |       |   | Current | Sample               | <u>CH0 / C</u>        | <del>:H4 / CH</del> | <u>8 / CH12</u> | 2 / CH16 |   |

|---------|-------|---|---------|----------------------|-----------------------|---------------------|-----------------|----------|---|

| 42H     | Bit   | 7 | 6       | 5                    | 4                     | 3                   | 2               | 1        | 0 |

| Access  | Value |   |         | Va                   | ariable (H            | HIGH byt            | e)              |          |   |

| R       | Note  |   | CH0 (0  | Group0) /<br>CH12 (0 | ′ CH4 (G<br>Group3) / |                     |                 | oup2) /  |   |

| Address |       |   | Current | Sample | <u>CH0 / C</u>        | <del>:H4 / CH</del> | <u>8 / CH12</u> | <u>/ CH16</u> |   |

|---------|-------|---|---------|--------|-----------------------|---------------------|-----------------|---------------|---|

| 43H     | Bit   | 7 | 6       | 5      | 4                     | 3                   | 2               | 1             | 0 |

| Access  | Value |   |         | V      | ariable (l            | _OW byt             | e)              |               |   |

| R       | Note  |   | CH0 (0  |        | ′ CH4 (G<br>Group3) / |                     |                 | oup2) /       |   |

| Address |       |   | Current         | Sample | e CH1 / C           | :H5 / CH | <u>9 / CH13</u> | <mark>6 / CH17</mark> |  |  |  |

|---------|-------|---|-----------------|--------|---------------------|----------|-----------------|-----------------------|--|--|--|

| 44H     | Bit   | 7 | 7 6 5 4 3 2 1 0 |        |                     |          |                 |                       |  |  |  |

| Access  | Value |   |                 | Va     | ariable (H          | HGH byt  | e)              |                       |  |  |  |

| R       | Note  |   | CH1 (0          |        | (CH5 (G<br>Group3), |          |                 | oup2) /               |  |  |  |

| Address |       |   | Current Sample CH1 / CH5 / CH9 / CH13 / CH17 |   |                       |         |    |         |  |  |  |  |

|---------|-------|---|----------------------------------------------|---|-----------------------|---------|----|---------|--|--|--|--|

| 45H     | Bit   | 7 | 7 6 5 4 3 2 1 0                              |   |                       |         |    |         |  |  |  |  |

| Access  | Value |   |                                              | V | ariable (l            | _OW byt | e) |         |  |  |  |  |

| R       | Note  |   | CH1 (0                                       |   | / CH5 (G<br>Group3) / |         |    | oup2) / |  |  |  |  |

| Address |       |   | <u>Current</u>  | Sample | <u>СН2 / С</u>       | H6 / CH1 | 10 / CH1 | <u>4 / CH18</u> |  |  |  |

|---------|-------|---|-----------------|--------|----------------------|----------|----------|-----------------|--|--|--|

| 46H     | Bit   | 7 | 7 6 5 4 3 2 1 0 |        |                      |          |          |                 |  |  |  |

| Access  | Value |   |                 | Va     | ariable (H           | HGH byt  | e)       |                 |  |  |  |

| R       | Note  |   | CH2 (G          |        | CH6 (Gr<br>Group3) / |          |          | roup2) /        |  |  |  |

| Address |       |   | Current Sample CH2 / CH6 / CH10 / CH14 / CH18 |                      |                      |  |  |          |  |  |  |

|---------|-------|---|-----------------------------------------------|----------------------|----------------------|--|--|----------|--|--|--|

| 47H     | Bit   | 7 | 7 6 5 4 3 2 1 0                               |                      |                      |  |  |          |  |  |  |

| Access  | Value |   | Variable (LOW byte)                           |                      |                      |  |  |          |  |  |  |

| R       | Note  |   | CH2 (G                                        | 6roup0) /<br>CH14 (0 | CH6 (Gr<br>Group3) / |  |  | roup2) / |  |  |  |

| Address |       |   | Current Sample CH3 / CH7 / CH11 / CH15 / CH19 |                      |                      |                       |                     |          |  |  |  |

|---------|-------|---|-----------------------------------------------|----------------------|----------------------|-----------------------|---------------------|----------|--|--|--|

| 48H     | Bit   | 7 | 7 6 5 4 3 2 1 0                               |                      |                      |                       |                     |          |  |  |  |

| Access  | Value |   | Variable (HIGH byte)                          |                      |                      |                       |                     |          |  |  |  |

| R       | Note  |   | CH3 (G                                        | 6roup0) /<br>CH15 (0 | CH7 (Gr<br>Group3) / | oup1) / (<br>/ CH19 ( | CH11 (Gi<br>Group4) | roup2) / |  |  |  |

| Address |       |   | <u>Current</u>      | Sample               | <u>СНЗ / С</u>       | H7 / CH1 | 1 / CH1 | <u>5 / CH19</u> |  |  |  |

|---------|-------|---|---------------------|----------------------|----------------------|----------|---------|-----------------|--|--|--|

| 49H     | Bit   | 7 | 7 6 5 4 3 2 1 0     |                      |                      |          |         |                 |  |  |  |

| Access  | Value |   | Variable (LOW byte) |                      |                      |          |         |                 |  |  |  |

| R       | Note  |   | CH3 (G              | 6roup0) /<br>CH15 (0 | CH7 (Gr<br>Group3) / |          |         | roup2) /        |  |  |  |

# 1.2.8 Long-Term Averages and Thresholds

The Long-Term averages, and each individual channels thresholds, of the current group are available here to read AND overwrite.

| Address |         | Lo      | ng-Term /                                                                     | Average | <u>СН0 / СН</u> | <u>4 / CH8</u> | / CH12    | <u>/ CH16</u> | <u>)</u> |  |  |

|---------|---------|---------|-------------------------------------------------------------------------------|---------|-----------------|----------------|-----------|---------------|----------|--|--|

| 83H     | Bit     | 7       | 6                                                                             | 5       | 4               | 3              | 2         | 1             | 0        |  |  |

|         | Value   | Touch T | <u>hreshold</u>                                                               | Prox Th | reshold         | Va             | riable (H | HIGH by       | /te)     |  |  |

| Access  | Default | 0       | 0                                                                             | 0       | 0               |                |           |               |          |  |  |

| R/W     | Note    |         | CH0 (Group0) / CH4 (Group1) / CH8 (Group2) /<br>CH12 (Group3) / CH16 (Group4) |         |                 |                |           |               |          |  |  |

| Address |       | Ŀ | Long-Term Average CH0 / CH4 / CH8 / CH12 / CH16 |  |                       |  |  |         |  |  |  |

|---------|-------|---|-------------------------------------------------|--|-----------------------|--|--|---------|--|--|--|

| 84H     | Bit   | 7 | 7 6 5 4 3 2 1 0                                 |  |                       |  |  |         |  |  |  |

| Access  | Value |   | Variable (LOW byte)                             |  |                       |  |  |         |  |  |  |

| R/W     | Note  |   | CH0 (0                                          |  | / CH4 (G<br>Group3) / |  |  | oup2) / |  |  |  |

| Address |         | Lo      | ng-Term /       | Average | <u>СН1 / СН</u>        | <u>5 / CH9</u> | / CH13    | / CH17 | <u> </u> |

|---------|---------|---------|-----------------|---------|------------------------|----------------|-----------|--------|----------|

| 85H     | Bit     | 7       | 6               | 5       | 4                      | 3              | 2         | 1      | 0        |

|         | Value   | Touch T | <u>hreshold</u> | Prox Th | nreshold               | Va             | riable (H | HGH by | /te)     |

| Access  | Default | 0       | 0               | 0       | 0                      |                |           |        |          |

| R/W     | Note    |         | CH1 (Gro<br>Cł  |         | 15 (Group<br>up3) / CH |                |           | p2) /  |          |

| Address |       | L | Long-Term Average CH1 / CH5 / CH9 / CH13 / CH17 |                      |                       |  |  |         |  |  |  |

|---------|-------|---|-------------------------------------------------|----------------------|-----------------------|--|--|---------|--|--|--|

| 86H     | Bit   | 7 | 7 6 5 4 3 2 1 0                                 |                      |                       |  |  |         |  |  |  |

| Access  | Value |   | Variable (LOW byte)                             |                      |                       |  |  |         |  |  |  |

| R/W     | Note  |   | CH1 ((                                          | Group0) /<br>CH13 (0 | / CH5 (G<br>Group3) / |  |  | oup2) / |  |  |  |

| Address |         | Lor     | ng-Term A       | verage ( | CH2 / CH               | 6 / CH1 | 0 / CH1   | 4 / CH1 | <u>8</u> |

|---------|---------|---------|-----------------|----------|------------------------|---------|-----------|---------|----------|

| 87H     | Bit     | 7       | 6               | 5        | 4                      | 3       | 2         | 1       | 0        |

|         | Value   | Touch T | <u>hreshold</u> | Prox Th  | reshold                | Va      | riable (H | HIGH by | /te)     |

| Access  | Default | 0       | 0               | 0        | 0                      |         |           |         |          |

| R/W     | Note    |         | CH2 (Gro<br>C   |          | l6 (Group<br>up3) / CH |         |           | up2) /  |          |

| Address |       | <u>Lo</u> | Long-Term Average CH2 / CH6 / CH10 / CH14 / CH18 |                                         |                      |  |  |          |  |  |  |

|---------|-------|-----------|--------------------------------------------------|-----------------------------------------|----------------------|--|--|----------|--|--|--|

| 88H     | Bit   | 7         | 7 6 5 4 3 2 1 0                                  |                                         |                      |  |  |          |  |  |  |

| Access  | Value |           | Variable (LOW byte)                              |                                         |                      |  |  |          |  |  |  |

| R/W     | Note  |           | CH2 (G                                           | ) (000000000000000000000000000000000000 | CH6 (Gr<br>Group3) / |  |  | roup2) / |  |  |  |

| Address |         | Lor     | ng-Term A     | verage (              | <u>CH3 / CH</u>        | 7 / CH1                         | 1 / CH1           | <u>5 / CH1</u> | <u>9</u> |

|---------|---------|---------|---------------|-----------------------|------------------------|---------------------------------|-------------------|----------------|----------|

| 89H     | Bit     | 7       | 6             | 5                     | 4                      | 3                               | 2                 | 1              | 0        |

|         | Value   | Touch T | hreshold      | Prox Th               | reshold                | Va                              | riable (H         | HIGH by        | /te)     |

| Access  | Default | 0       | 0             | 0                     | 0                      |                                 |                   |                |          |

| R/W     | Note    |         | CH3 (Gro<br>C | up0) / CH<br>H15 (Gro | l7 (Group<br>up3) / CH | 1) / CH <sup>2</sup><br>19 (Gro | 11 (Grou<br>oup4) | up2) /         |          |

| Address |       | <u>Lo</u> | ong-Tern            | n Averaç             | <mark>ge CH3 /</mark> | СН7 / С                | H11 / CH            | 115 / CH | <u>19</u> |  |  |  |

|---------|-------|-----------|---------------------|----------------------|-----------------------|------------------------|---------------------|----------|-----------|--|--|--|

| 8AH     | Bit   | 7         | 7 6 5 4 3 2 1 0     |                      |                       |                        |                     |          |           |  |  |  |

| Access  | Value |           | Variable (LOW byte) |                      |                       |                        |                     |          |           |  |  |  |

| R/W     | Note  |           | CH3 (G              | 6roup0) /<br>CH15 (0 | CH7 (Gr<br>Group3) /  | oup1) / 0<br>/ CH19 (0 | CH11 (Gi<br>Group4) | roup2) / |           |  |  |  |

## 1.2.9 Device Settings

An attempt is made so that the commonly used settings are situated closer to the top of the memory block. Settings that are regarded as more 'once-off' are placed further down.

| Address |         |        | <u>UI                                    </u> | <u>Settings 0</u> | (UI_SETT       | INGS0)                |                        |           |   |  |

|---------|---------|--------|-----------------------------------------------|-------------------|----------------|-----------------------|------------------------|-----------|---|--|

| C4H     | Bit     | 7      | 7 6 5 4 3 2 1                                 |                   |                |                       |                        |           |   |  |

| Access  | Name    | RESEED | ATI_MODE                                      | PROX<br>RANGE     | TOUCH<br>RANGE | FORCE<br>PROX<br>MODE | FORCE<br>TOUCH<br>MODE | <u>ND</u> | 0 |  |

| R/W     | Default | 0      | 0                                             | 1                 | 0              | 0                     | 0                      | 1         | 0 |  |

| Address |         |   |   |   | Powe | r Settings (P | OWER SETT | NGS)       |            |

|---------|---------|---|---|---|------|---------------|-----------|------------|------------|

| C5H     | Bit     | 7 | 6 | 5 | 4    | 3             | 2         | 1          | 0          |

| Access  | Name    | ~ | ~ | ~ | ~    | <u>SLEEP</u>  | MAIN_OSC  | <u>LP1</u> | <u>LP0</u> |

| R/W     | Default | ~ | ~ | ~ | ~    | 0             | 0         | 0          | 0          |

| Address |         |              | ProxSense <sup>®</sup> Module Settings 1 (PROX_SETTINGS_1) |       |       |      |        |        |        |  |  |  |  |  |  |

|---------|---------|--------------|------------------------------------------------------------|-------|-------|------|--------|--------|--------|--|--|--|--|--|--|

| C6H     | Bit     | 7            | 6                                                          | 5     | 4     | 3    | 2      | 1      | 0      |  |  |  |  |  |  |

| Access  | Name    | <u>CXVSS</u> | <u>ZC_EN</u>                                               | HALT1 | HALT0 | AUTO | CXDIV2 | CXDIV1 | CXDIV0 |  |  |  |  |  |  |

| R/W     | Default | 1            | 0                                                          | 0     | 1     | 0    | 0      | 1      | 0      |  |  |  |  |  |  |

| Address |         |   |                            | <b>ProxSense</b> | <sup>®</sup> Module | Settings 2           | 2 (PROX_SE      | TTINGS_2)             |                       |

|---------|---------|---|----------------------------|------------------|---------------------|----------------------|-----------------|-----------------------|-----------------------|

| C7H     | Bit     | 7 | 6                          | 5                | 4                   | 3                    | 2               | 1                     | 0                     |

| Access  | Name    | 1 | <u>SHIELD</u><br><u>EN</u> | STOP_<br>COMMS   | ACK_<br>RESET       | <u>SKIP_</u><br>CONV | ACF_<br>DISABLE | <u>LTN</u><br>DISABLE | <u>WDT</u><br>DISABLE |

| R/W     | Default | ~ | 0                          | 0                | 0                   | 0                    | 0               | 0 <sup>Note 1</sup>   | 1                     |

Note1: The LTN filter has a limitation: it is default ON, but it is recommended that this feature be disabled by the user (setting the bit).

| Address |         |              |      |      | ATI Mul | tiplier ( | C (ATI_ | MULT1) | 2   |     |

|---------|---------|--------------|------|------|---------|-----------|---------|--------|-----|-----|

| C8H     | Bit     |              | 7    | 6    | 5       | 4         | 3       | 2      | 1   | 0   |

| Access  | Name    | If Group = 0 | CH3  |      | CH2     |           | CH1     |        | CI  | HO  |

| R/W     |         | If Group = 1 | CH7  |      | CH6     |           | CH5     |        | CH4 |     |

|         |         | If Group = 2 | C⊦   | CH11 |         | 110       | Cł      | -19    | CI  | -18 |

|         |         | If Group = 3 | CH   | 115  | CH14    |           | CH      | 113    | CH  | 112 |

|         |         | If Group = 4 | CH19 |      | CH      | 118       | CH      | 117    | CH  | 116 |

|         | Default |              | 0    | 0    | 0       | 0         | 0       | 0      | 0   | 0   |

| <b>U</b> |

|----------|

| ×        |

C9H Access

Address

R/W

|       |      | ATI Multiplier I (ATI_MULT2) |      |      |              |        |        |   |  |  |  |  |  |  |  |

|-------|------|------------------------------|------|------|--------------|--------|--------|---|--|--|--|--|--|--|--|

| Bit   | 7    | 6                            | 5    | 4    | 3            | 2      | 1      | 0 |  |  |  |  |  |  |  |

| Name  | CH3  | CH2                          | CH1  | CH0  | If Group = 0 |        |        |   |  |  |  |  |  |  |  |

|       | CH7  | CH6                          | CH5  | CH4  |              | lf Gro | up = 1 |   |  |  |  |  |  |  |  |

|       | CH11 | CH10                         | CH9  | CH8  |              | lf Gro | up = 2 |   |  |  |  |  |  |  |  |

|       | CH15 | CH14                         | CH13 | CH12 |              | lf Gro | up = 3 |   |  |  |  |  |  |  |  |

|       | CH19 | CH18                         | CH17 | CH16 |              | lf Gro | up = 4 |   |  |  |  |  |  |  |  |

| Defau | t O  | 0                            | 0    | 0    | ~            | ~      | ~      | ~ |  |  |  |  |  |  |  |

| Address     |       |              |        | AT | I Compo | ensatio | n <mark>Settin</mark> | g (ATI_ | <u>C0)</u> |   |  |  |

|-------------|-------|--------------|--------|----|---------|---------|-----------------------|---------|------------|---|--|--|

| САН         | Bit   |              | 7      | 6  | 5       | 4       | 3                     | 2       | 1          | 0 |  |  |

| Access      | Value | If Group = 0 | СНО    |    |         |         |                       |         |            |   |  |  |

| R/W         |       | If Group = 1 | CH4    |    |         |         |                       |         |            |   |  |  |

| . <u></u> . |       | If Group = 2 |        |    |         | Cł      | 48                    |         |            |   |  |  |

|             |       | If Group = 3 |        |    |         | C⊦      | 112                   |         |            |   |  |  |

|             |       | If Group = 4 | 4 CH16 |    |         |         |                       |         |            |   |  |  |

| Address |       |              |      | AT | I Compo | ensatio | n Settin | g (ATI | <u>C1)</u> |   |  |  |

|---------|-------|--------------|------|----|---------|---------|----------|--------|------------|---|--|--|

| СВН     | Bit   |              | 7    | 6  | 5       | 4       | 3        | 2      | 1          | 0 |  |  |

| Access  | Value | If Group = 0 | CH1  |    |         |         |          |        |            |   |  |  |

| R/W     |       | If Group = 1 | CH5  |    |         |         |          |        |            |   |  |  |

|         |       | If Group = 2 |      |    |         | Cł      | -19      |        |            |   |  |  |

|         |       | If Group = 3 |      |    |         | CH      | 113      |        |            |   |  |  |

|         |       | If Group = 4 | CH17 |    |         |         |          |        |            |   |  |  |

| Address |       |              |                 | <u>AT</u> | I Compe | ensatio | n <mark>Settin</mark> | g (ATI | <u>C2)</u> |  |  |  |  |

|---------|-------|--------------|-----------------|-----------|---------|---------|-----------------------|--------|------------|--|--|--|--|

| ССН     | Bit   |              | 7 6 5 4 3 2 1 0 |           |         |         |                       |        |            |  |  |  |  |

| Access  | Value | If Group = 0 | CH2             |           |         |         |                       |        |            |  |  |  |  |

| R/W     |       | If Group = 1 | CH6             |           |         |         |                       |        |            |  |  |  |  |

|         |       | If Group = 2 |                 |           |         | CH      | 110                   |        |            |  |  |  |  |

|         |       | If Group = 3 |                 |           |         | CH      | 114                   |        |            |  |  |  |  |

|         |       | If Group = 4 | CH18            |           |         |         |                       |        |            |  |  |  |  |

| Address   |       |              |                 | AT | I Compe | ensatio | n <mark>Settin</mark> | g (ATI_ | <u>C3)</u> |  |  |  |  |

|-----------|-------|--------------|-----------------|----|---------|---------|-----------------------|---------|------------|--|--|--|--|

| CDH       | Bit   |              | 7 6 5 4 3 2 1 0 |    |         |         |                       |         |            |  |  |  |  |

| Access    | Value | If Group = 0 | CH3             |    |         |         |                       |         |            |  |  |  |  |

| R/W       |       | If Group = 1 | CH7             |    |         |         |                       |         |            |  |  |  |  |

| . <u></u> |       | If Group = 2 |                 |    |         | C⊦      | 111                   |         |            |  |  |  |  |

|           |       | If Group = 3 |                 |    |         | C⊦      | 115                   |         |            |  |  |  |  |

|           |       | If Group = 4 | CH19            |    |         |         |                       |         |            |  |  |  |  |

| Address |         |   |   |   | <u>Shie</u> | eld Se | ttings (SHLD | <u>SETTINGS)</u> |       |

|---------|---------|---|---|---|-------------|--------|--------------|------------------|-------|

| CEH     | Bit     | 7 | 6 | 5 | 4           | 3      | 2            | 1                | 0     |

| Access  | Name    | ~ | ~ | ~ | ~           | ~      | SHLD2        | SHLD1            | SHLD0 |

| R/W     | Default | 0 | 0 | 0 | 0           | 0      | 0            | 0                | 0     |

\* Note this byte will be ignored if <u>SHIELD\_EN</u> (<u>PROX\_SETTINGS\_2</u><6>) is set (i.e. if automated shield is selected).

| Address |         |   |   | U | Inused (I | keep 00H | ) |   |   |

|---------|---------|---|---|---|-----------|----------|---|---|---|

| CFH     | Bit     | 7 | 6 | 5 | 4         | 3        | 2 | 1 | 0 |

| Access  | Name    | ~ | ~ | 0 | 0         | 0        | 0 | 0 | 0 |

| R/W     | Default | ~ | ~ | 0 | 0         | 0        | 0 | 0 | 0 |

| Address |         |           | <u>Cx</u> | Co | nfig | guration (C) | <u>(CONFIG)</u> |                      |           |

|---------|---------|-----------|-----------|----|------|--------------|-----------------|----------------------|-----------|

| D0H     | Bit     | 7         | 6         | 5  | 4    | 3            | 2               | 1                    | 0         |

| Access  | Name    | CX_GPIO_1 | CX_GPIO_0 | ~  | ~    | Prox Mode    | Group Sele      | ection ( <u>PM_C</u> | X_SELECT) |

|         |         |           |           |    |      | GROUP4       | GROUP3          | GROUP2               | GROUP1    |

| R/W     | Default | 0         | 0         | ~  | ~    | 1            | 1               | 1                    | 1         |

| Address |         |   | DEFAULT_COMMS_POINTER |           |            |           |             |    |   |  |  |  |

|---------|---------|---|-----------------------|-----------|------------|-----------|-------------|----|---|--|--|--|

| D1H     | Bit     | 7 | 6                     | 5         | 4          | 3         | 2           | 1  | 0 |  |  |  |

| Access  | Default |   | 1                     | 0H (Begir | nning of D | evice Spe | ecific Data | a) |   |  |  |  |

| R/W     |         |   |                       |           |            |           |             |    |   |  |  |  |

| Address |         |   | <u>Indiv</u> | idual Cha | annel Dis | able (CH | AN ACT | <u>VE0)</u> |     |

|---------|---------|---|--------------|-----------|-----------|----------|--------|-------------|-----|

| D2H     | Bit     | 7 | 6            | 5         | 4         | 3        | 2      | 1           | 0   |

| Access  | Name    | ~ | ~            | ~         | ~         | СНЗ      | CH2    | CH1         | CH0 |

| R/W     | Default | ~ | ~            | ~         | ~         | 0        | 0      | 1           | 1   |

\*Note: Only group 0 and 1 are default on, this is because with more than 2 channels active, the AC Filter isn't sampled at the optimal frequency, and is thus less effective.

| Address |         |   | Individual Channel Disable (CHAN_ACTIVE1) |   |   |     |     |     |     |  |  |

|---------|---------|---|-------------------------------------------|---|---|-----|-----|-----|-----|--|--|

| D3H     | Bit     | 7 | 6                                         | 5 | 4 | 3   | 2   | 1   | 0   |  |  |

| Access  | Name    | ~ | ~                                         | ~ | ~ | CH7 | CH6 | CH5 | CH4 |  |  |

| R/W     | Default | ~ | ~                                         | ~ | ~ | 1   | 1   | 1   | 1   |  |  |

| Address |         |   | Individual Channel Disable (CHAN_ACTIVE2) |   |   |      |      |     |     |  |  |

|---------|---------|---|-------------------------------------------|---|---|------|------|-----|-----|--|--|

| D4H     | Bit     | 7 | 6                                         | 5 | 4 | 3    | 2    | 1   | 0   |  |  |

| Access  | Name    | ~ | ~                                         | ~ | ~ | CH11 | CH10 | CH9 | CH8 |  |  |

| R/W     | Default | ~ | ~                                         | ~ | ~ | 1    | 1    | 1   | 1   |  |  |

| Address |         |   | Individual Channel Disable (CHAN_ACTIVE3) |   |   |      |      |      |      |  |  |  |

|---------|---------|---|-------------------------------------------|---|---|------|------|------|------|--|--|--|

| D5H     | Bit     | 7 | 6                                         | 5 | 4 | 3    | 2    | 1    | 0    |  |  |  |

| Access  | Name    | ~ | ~                                         | ~ | ~ | CH15 | CH14 | CH13 | CH12 |  |  |  |

| R/W     | Default | ~ | ~                                         | ~ | ~ | 1    | 1    | 1    | 1    |  |  |  |

| Address |         |   | Individual Channel Disable (CHAN_ACTIVE4) |   |   |      |      |      |      |  |  |  |

|---------|---------|---|-------------------------------------------|---|---|------|------|------|------|--|--|--|

| D6H     | Bit     | 7 | 6                                         | 5 | 4 | 3    | 2    | 1    | 0    |  |  |  |

| Access  | Name    | ~ | ~                                         | ~ | ~ | CH19 | CH18 | CH17 | CH16 |  |  |  |

| R/W     | Default | ~ | ~                                         | ~ | ~ | 1    | 1    | 1    | 1    |  |  |  |

| Address |         |   | Individual Channel Reseed (CHAN RESEED0) |   |   |     |     |     |     |  |  |  |

|---------|---------|---|------------------------------------------|---|---|-----|-----|-----|-----|--|--|--|

| D7H     | Bit     | 7 | 6                                        | 5 | 4 | 3   | 2   | 1   | 0   |  |  |  |

| Access  | Name    | ~ | ~                                        | ~ | ~ | СНЗ | CH2 | CH1 | CH0 |  |  |  |

| R/W     | Default | ~ | ~                                        | ~ | ~ | 0   | 0   | 0   | 0   |  |  |  |

| Address |         |   | Individual Channel Reseed (CHAN_RESEED1) |   |   |     |     |     |     |  |  |

|---------|---------|---|------------------------------------------|---|---|-----|-----|-----|-----|--|--|

| D8H     | Bit     | 7 | 6                                        | 5 | 4 | 3   | 2   | 1   | 0   |  |  |

| Access  | Name    | ~ | ~                                        | ~ | ~ | CH7 | CH6 | CH5 | CH4 |  |  |

| R/W     | Default | ~ | ~                                        | ~ | ~ | 0   | 0   | 0   | 0   |  |  |

| Address |      |      | Individual Channel Reseed (CHAN RESEED2) |   |   |   |      |      |     |     |  |  |

|---------|------|------|------------------------------------------|---|---|---|------|------|-----|-----|--|--|

| D9H     | Bi   | t    | 7                                        | 6 | 5 | 4 | 3    | 2    | 1   | 0   |  |  |

| Access  | Nar  | ne   | ~                                        | ~ | ~ | ~ | CH11 | CH10 | CH9 | CH8 |  |  |

| R/W     | Defa | ault | ~                                        | ~ | ~ | ~ | 0    | 0    | 0   | 0   |  |  |

| Address |         |   | Individual Channel Reseed (CHAN_RESEED3) |   |   |      |      |      |      |  |  |  |

|---------|---------|---|------------------------------------------|---|---|------|------|------|------|--|--|--|

| DAH     | Bit     | 7 | 6                                        | 5 | 4 | 3    | 2    | 1    | 0    |  |  |  |

| Access  | Name    | ~ | ~                                        | 2 | ~ | CH15 | CH14 | CH13 | CH12 |  |  |  |

| R/W     | Default | ~ | ~                                        | ~ | ۲ | 0    | 0    | 0    | 0    |  |  |  |

| Address |         |   | Individual Channel Reseed (CHAN_RESEED4) |   |   |      |      |      |      |  |  |  |

|---------|---------|---|------------------------------------------|---|---|------|------|------|------|--|--|--|

| DBH     | Bit     | 7 | 6                                        | 5 | 4 | 3    | 2    | 1    | 0    |  |  |  |

| Access  | Name    | ~ | ~                                        | ~ | ~ | CH19 | CH18 | CH17 | CH16 |  |  |  |

| R/W     | Default | ~ | ~                                        | ~ | ~ | 0    | 0    | 0    | 0    |  |  |  |

| Address |         |   | Auto ATI Target                               |   |   |   |   |   |   |

|---------|---------|---|-----------------------------------------------|---|---|---|---|---|---|

| DCH     | Bit     | 7 | 6                                             | 5 | 4 | 3 | 2 | 1 | 0 |

| Access  | Value   |   | Variable (HIGH Byte)                          |   |   |   |   |   |   |

| R/W     | Default |   | 04H (giving a Target value of = 1024 decimal) |   |   |   |   |   |   |

| Address |         |                                               | Auto ATI Target     |   |   |   |   |   |   |

|---------|---------|-----------------------------------------------|---------------------|---|---|---|---|---|---|

| DDH     | Bit     | 7                                             | 6                   | 5 | 4 | 3 | 2 | 1 | 0 |

| Access  | Value   |                                               | Variable (LOW Byte) |   |   |   |   |   |   |

| R/W     | Default | 00H (giving a Target value of = 1024 decimal) |                     |   |   |   |   |   |   |

| Address |      |                                         | <u>I/O Port</u>                                                                                                 |   |   |   |   |   |   |

|---------|------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|

| DEH     | Bit  | 7                                       | 6                                                                                                               | 5 | 4 | 3 | 2 | 1 | 0 |

| Access  | Name | GPIO_7                                  | GPIO_7         GPIO_6         GPIO_5         GPIO_4         GPIO_3         GPIO_2         GPIO_1         GPIO_0 |   |   |   |   |   |   |

| R/W     |      | I/O's can be read, or set/cleared here. |                                                                                                                 |   |   |   |   |   |   |

| Address |         |        | <u>I/O Tris</u> |        |        |        |        |        |        |

|---------|---------|--------|-----------------|--------|--------|--------|--------|--------|--------|

| DFH     | Bit     | 7      | 6               | 5      | 4      | 3      | 2      | 1      | 0      |

| Access  | Name    | GPIO_7 | GPIO_6          | GPIO_5 | GPIO_4 | GPIO_3 | GPIO_2 | GPIO_1 | GPIO_0 |

| R/W     | Default | 1      | 1               | 1      | 1      | 1      | 1      | 1      | 1      |

NOTE: If the pins are used as Cx channels, they MUST be set to inputs in the TRIS register

# **1.3 Memory Map Description**

## 1.3.1 Device Information

### Product Number

The product number for the IQS316 is 27 (decimal).

### Version Number

The version number of the device ROM can be read in this byte.

### 1.3.2 Device Specific Data

### XY Info1 (UI\_FLAGS0)

Bit 7: **SHOW RESET**: This bit can be read to determine whether a reset occurred on the device since the <u>ACK\_RESET</u> bit has been set. The value of SHOW\_RESET can be set to '0' by writing a '1' in the ACK\_RESET bit in the PROX\_SETTINGS\_2 byte. 0 = No reset has occurred since last cleared 1 = Reset has occurred Bit 6: **MODE\_INDICATOR:** Indicates current mode of charging 0 = Currently in Prox Mode 1 = Currently in Touch Mode Bit 5:3: Unused Bit 2: ATI BUSY: Status of automated ATI routine 0 = Auto ATI is not busy 1 = Auto ATI in progress **RESEED BUSY:** Global Channel Reseed Status Bit 1:

- 0 = Reseed is not busy

- 1 = Reseed is currently taking place

- *Bit 0:* **NOISE:** This bit indicates the presence of noise interference.

- 0 = Current cycle has not detected the presence of noise

- 1 = Current cycle has detected the presence of noise

### 1.3.3 **Proximity Status Bytes**

#### **Proximity Status**

The proximity status of the channels relating to the current group can be read here. The current group can be determined by reading the <u>Group Number</u> register. The channels and group numbers relate as shown in Table 1.2.

| Current Group Number | Channels available        |  |  |  |

|----------------------|---------------------------|--|--|--|

| 0                    | CH0 / CH1 / CH2 / CH3     |  |  |  |

| 1                    | CH4 / CH5 / CH6 / CH7     |  |  |  |

| 2                    | CH8 / CH9 / CH10 / CH11   |  |  |  |

| 3                    | CH12 / CH13 / CH14 / CH15 |  |  |  |

| 4                    | CH16 / CH17 / CH18 / CH19 |  |  |  |

#### Table 1.2Channel data available

### 1.3.4 Touch Status Bytes

### Touch Status

The touch status of the channels relating to the current group can be read here. The current group can be determined by reading the <u>Group Number</u> register. The channels and group numbers relate as shown in Table 1.2.

#### 1.3.5 Halt Bytes

#### Halt Status

The halt status of the channels relating to the current group can be read here. The current group can be determined by reading the <u>Group Number</u> register. The channels and group numbers relate as shown in Table 1.2.

#### 1.3.6 Active Bytes

#### Group Number

The group number that can be read in this byte indicates which group's data is currently available. Group 0 is the Prox Mode group, and Group 1-4 are the Touch Mode groups.

### 1.3.7 <u>Current Samples</u>

The Current Samples for the current group can be read in their respective addresses. The HIGH bytes and LOW bytes are found in consecutive addresses.

## 1.3.8 Long-Term Averages & Touch/Prox Thresholds

The LTA values for the current group can be read in their respective addresses. The HIGH bytes and LOW bytes are found in consecutive addresses.

The first four bits (high nibble) of each LTA HIGH Byte is the Prox and Touch Thresholds for the respective channel. Care must be taken when overwriting a LTA that the required settings are also included in the HIGH byte.

#### LTA HIGH Byte

- *Bit 7-6:* <u>**Touch Threshold**</u>: The value of these two bits, together with the global Touch Range bit determines the Touch Threshold, as shown in Table 1.3.

- *Bit 5-4:* **Prox Threshold:** The value of these two bits, together with the Prox Range bit determines the Prox Threshold, as shown in 0.

- Bit 3-0: LTA<11:8>: The upper 4 bits of the LTA.

| Touch Threshold <1:0> | TOUCH_RANGE = 0  | TOUCH_RANGE = 1 |  |  |  |

|-----------------------|------------------|-----------------|--|--|--|

| Touch Threshold <1:0> | Touch Threshold: |                 |  |  |  |

| 00                    | 1/32 (default)   | 4/16            |  |  |  |

| 01                    | 1/16             | 6/16            |  |  |  |

| 10                    | 2/16             | 8/16            |  |  |  |

| 11                    | 3/16             | 10/16           |  |  |  |

### Table 1.3Touch Threshold Values

Table 1.4Prox Threshold Values

| Drow Thread and the  | PROX_RANGE = 0 | PROX_RANGE = 1 |  |  |  |

|----------------------|----------------|----------------|--|--|--|

| Prox Threshold <1:0> | Prox Threshold |                |  |  |  |

| 00                   | 2              | 8 (default)    |  |  |  |

| 01                   | 3              | 16             |  |  |  |

| 10                   | 4              | 20             |  |  |  |

| 11                   | 6              | 30             |  |  |  |

### LTA LOW Byte

Bit 7-0: LTA<7:0>: The lower byte of the LTA.

### **1.3.9 Device Settings**

### UI Settings 0 (UI\_SETTINGS0)

- *Bit 7:* **RESEED**: Reseed the LTA filter. This can be used to adapt to an abrupt environment change, where the filter is too slow to track this change. Note that with the Short and Long Halt selections, an automatic Reseed will be performed when the halt time has expired, thus automatically adjusting to the new surroundings.

- 0 = Do not reseed

- 1 = Reseed (this is a global reseed)

- *Bit 6:* <u>ATI\_MODE</u>: This selects which mode to perform the auto ATI routine on, and the <u>AUTO\_ATI</u> enable bit initiates the routine.

- 0 = Automated ATI will apply to Prox-Mode channels

- 1 = Automated ATI will apply to Touch-Mode channels

- *Bit 5:* **PROX RANGE:** Selects between two Prox threshold sets. The range is a global setting and applies to all channels; whereby each channel can then individually be setup to a custom threshold value within this selected range.

- 0 = Lower range threshold set

- 1 = Higher range threshold set

- *Bit 4:* <u>**TOUCH RANGE**</u>: Selects between two touch threshold sets. The range is a global setting and applies to all channels; whereby each channel can then individually be setup to a custom threshold value within this selected range.

- 0 = Lower range threshold set

- 1 = Higher range threshold set

- *Bit 3:* **FORCE PROX MODE**: Force charging to Prox Mode. If this bit is set, automatic transitions between Prox and Touch Mode are overwritten.

- 0 = Normal Operation

- 1 = Only Prox Mode charging

- *Bit 2:* **FORCE TOUCH MODE:** Force charging to Touch Mode. If this bit is set, automatic transitions between Prox and Touch Mode are overwritten. Note: this bit takes precedence over Bit 3.

- 0 = Normal Operation

- 1 = Only Touch Mode charging

- *Bit 1:* <u>ND</u>: Noise Detection Enable. This setting is used to enable the on-chip noise detection circuitry. With noise detected, the noise affected samples will be ignored, and have no effect on the Prox, touch or LTA calculations. The **NOISE** bit will appropriately be set as indication of the noise status.

- 0 = Disable noise detection

- 1 = Enable noise detection

- Bit 0: Internal: This bit should always keep the value of 0

### Power Settings (POWER\_SETTINGS)

#### Bit 7:4: Unused

*Bit 3:* <u>SLEEP</u>: This bit puts the IC in SLEEP mode. Sleep is entered after termination of the communication window. No processing is done in the sleep state. This function is available in both SPI and I<sup>2</sup>C. In SPI, to wake the device from sleep, the /SS line is pulled low, thus selecting the device, whereby waking it from sleep. Communication with the device is then immediately resumed.

In I<sup>2</sup>C, to wake the device, the master simply is required to begin communication with the device.

In both cases, when the IC is woken from sleep, the firmware returns to the same communication window that was last used to put the device to sleep, thus no new sample data is available. Note that if the IC has been in SLEEP for a considerable time, it is recommended to reseed the channels, if no interaction is assumed.

- 0 = No effect

- 1 = Puts device in sleep mode

#### Bit 2: <u>MAIN\_OSC</u>: Select the frequency of the main oscillator

0 = 8MHz

- 1 = 4MHz (not recommended)

- Bit 1-0: Low Power (LP) options

- 00 = Normal Power

- $01 = LP1 \sim 100ms$  charging

- $10 = LP2 \sim 200ms$  charging

- 11 = LP3 ~ 300ms charging

#### ProxSense<sup>®</sup> Module Settings 1 (PROX\_SETTINGS\_1)

- *Bit 7:* <u>CXVSS</u>: Ground Cx channels when inactive. The default and recommended setting is grounded. The result is illustrated by means of an example. If for instance Group 1 is charging, all surrounding sensing lines not part of Group 1 are grounded, and thus in a defined state. If the Cx's are set to float, then their state is unknown, and the sensors influence each other greatly, which is not ideal.

- 0 = Cx's float

- 1 = Cx's grounded

- *Bit 6:* <u>**ZC EN**</u>: Enable zero-cross (ZC) triggered conversions. An input signal must be connected to the ZC\_IN I/O to synchronise the charging to. This is occasionally used in high AC noise applications, whereby synchronising the charging to the AC, the noise is reduced. This input allows the timing of the conversions to be accurately controlled. Possibly the conversions can be sliced between noise events to keep the samples noise free.

- 0 = No Zero-Cross signal implemented

- 1 = Conversions synchronised to ZC\_IN

- Bit 5-4: HALT: LTA Filter Halt selections

00 = Short (LTA filter halts for ~20 seconds, then reseeds)

01 = Long (LTA filter halts for ~40 seconds, then reseeds)

- 10 = Never (LTA filter never halts)

- 11 = Always (LTA filter is halted permanently)

- *Bit 3:* <u>AUTO\_ATI</u>: Enable the automated ATI routine. By enabling this bit, the device will perform an automated ATI routine on the selected groups (selected by <u>ATI\_MODE</u>), and will attempt to reach the target setup in <u>AUTO-ATI Target</u>. Note that the ATI routine is only started after the communication window is closed, and thus the <u>ATI\_BUSY</u> bit will only be set in the following communication window.

- 0 = No action

- 1 = Begin auto ATI routine

- *Bit 2-0:* <u>CXDIV[2:0]</u>: Selection bits for charge transfer frequency

| MAIN_O  | SC = 4MHz               | MAIN_OSC = 8MHz |                         |  |

|---------|-------------------------|-----------------|-------------------------|--|

| CXDIV   | Conversion<br>Frequency | CXDIV           | Conversion<br>Frequency |  |

| 000     | 2MHz                    | 000             | 4MHz                    |  |

| 001     | 1MHz                    | 001             | 2MHz                    |  |

| 010     | 500kHz                  | 010             | 1MHz (default)          |  |

| 011     | 250kHz                  | 011             | 500kHz                  |  |

| 100     | 125kHz                  | 100             | 250kHz                  |  |

| 101-111 | 62.5kHz                 | 101-111         | 125kHz                  |  |

Table 1.5

Charge transfer frequency

The charge transfer frequency is a very important parameter. Dependant on the design application, the device frequency must be optimised. For example, if keys are to be used in an environment where steam or water droplets could form on the keys, a higher transfer frequency improves immunity. Also, if a sensor antenna is a very large object/size, then a lower frequency must be selected since the capacitance of the sensor is large, and a lower frequency is required to allow effective capacitive sensing on the sensor.

# ProxSense<sup>®</sup> Module Settings 2 (PROX\_SETTINGS\_2)

Bit 7: Unused

*Bit 6:* <u>SHIELD EN</u>: Automatic shield implementation. Each group will have a shield setup automatically on the two shield outputs, according to Table 1.6.

| Azoteq |

|--------|

|--------|

| Table 1.6Automated S | hield Channels |

|----------------------|----------------|

|----------------------|----------------|

| 14010 110 |        |        |

|-----------|--------|--------|

| Group     | SHLD_A | SHLD_B |

| 0         | CxA0   | CxB0   |

| 1         | CxA0   | CxB0   |

| 2         | CxA1   | CxB1   |

| 3         | CxA2   | CxB2   |

| 4         | CxA3   | CxB3   |

0 = Shield is set by <u>SHIELD\_SETTING</u> byte

- 1 = Shield is automatically loaded according to Table 1.6

- *Bit 5:* <u>STOP COMMS</u>: Skip the SPI/I<sup>2</sup>C communication window. This can be used if the master does not want to service the IQS316 every charge cycle. Normal operation of the IC continues, and only the communication window is bypassed. Only when the master initiates, or when a Prox is sensed, will the communication be resumed.

0 = Normal Communication

- 1 = Communication aborted until Prox detected, or master forces a resume

- Bit 4: <u>ACK\_RESET</u>: Acknowledge '<u>SHOW\_RESET</u>'.

0 = Nothing

- 1 = Clear the flag **<u>SHOW\_RESET</u>** (send only once)

- *Bit 3:* <u>SKIP CONV</u>: Don't perform conversion. This can be used, for example if settings for all the groups are to be written. The current groups' settings can be completed, and the communication window can then be terminated. The device then loads the next groups' data (without performing a conversion), and the next communication window is available. Stepping through all the groups can thus be done without the need to wait for a conversion to complete.

0 = Normal operation

1 = Skip conversions (Load next group's data and return to communication window)

- *Bit 2:* <u>ACF DISABLE</u>: Disable the AC Filter on Group 0.

- 0 = AC Filter is enabled

- 1 = AC Filter is disabled

- Bit 1: <u>LTN\_DISABLE</u>: Disable the LTN Filter on Group 0.

- 0 = LTN Filter is enabled

- 1 = LTN Filter is disabled (recommended due to device limitation)

Bit 0:

WDT\_DISABLE: Device watchdog timer (WDT) disable.

0 = Enabled

1 = Disabled

## ATI Multiplier C (ATI\_MULT1)

The ATI Multiplier and ATI Compensation bits allow the controller to be compatible with a large range of sensors, and in many applications with different environments. ATI allows the user to maintain a specific sample value on all channels. The ATI Multiplier parameters would produce the largest changes in sample values and can be thought of as the high bits of ATI. The ATI Compensation bits are used to influence the sample values on a smaller scale to provide precision when balancing all channels as close as possible to the target. The ATI Multiplier parameters are further grouped into two parameters namely ATI Multiplier C and ATI Multiplier I. ATI multiplier I consists of a single bit and has the biggest effect on the sample value and can be considered as the highest bit of the ATI parameters.

The ATI\_MULT1 byte contains the ATI Multipliers C settings for all channels of the current group. Each channel has two ATI Multiplier C bits where the value of '11' would provide the highest CS value and the value of '00' would provide the lowest.

#### ATI Multiplier I (ATI\_MULT2)

The ATI Multiplier I bit is the ATI bit which would make the largest adjustment to the sample value. The ATI\_MULT3 byte contains the ATI Multiplier I settings for all the channels in the current group, where a value of '1' would produce the largest sample value and a value of '0' would produce the smallest sample value.

### ATI Compensation Settings

The ATI Compensation parameter can be configured for each channel in a range between 0-255 (decimal). The ATI compensation bits can be used to make small adjustments of the sample values of the individual channels.

### Shield Settings (SHLD\_SETTINGS)

If the <u>SHIELD EN</u> bit is set, the value written to the <u>SHLD SETTINGS</u> register is simply ignored. Otherwise the shield can be manually configured here.

The <u>SHLD SETTINGS</u> byte is used to enable or disable the two active shields. Bit 0-2 control which sensor lines are to be shielded on **SHLD\_A** and **SHLD\_B**. By default the shields are disabled with <u>SHLD SETTINGS</u> = 0. Manual configuration is implemented as shown in Table 1.7.

| Table 1.7          | SHLD_A and SHLD_             | B configuration              |

|--------------------|------------------------------|------------------------------|

| SHLD_SETTINGS<2:0> | SHLD_A input<br>connected to | SHLD_B input<br>connected to |

| 000                | SHLDL off (default)          | SHLDR off (default)          |

| 001                | CxA6                         | CxB6                         |

| 010                | CxA5                         | CxB5                         |

| 011                | CxA4                         | CxB4                         |

| 100                | CxA3                         | CxB3                         |

| 101                | CxA2                         | CxB2                         |

| 110                | CxA1                         | CxB1                         |

| 111                | CxA0                         | CxB0                         |

## Table 1.7 SHLD\_A and SHLD\_B configuration

IQ Switch<sup>®</sup> ProxSense<sup>®</sup> Series

### Cx Configuration (CX\_CONFIG)

Bit 7:

<u>CX GPIO 1</u>: Cx or I/O selection.

0 = CxA7, CxA6, CxB7 and CxB6 are used as sensor lines

1 = GPIO\_7, GPIO\_6, GPIO\_5 and GPIO\_4 are implemented as I/O's

### Table 1.8Upper Nibble of I/O Port Selection

| CX_GPIO_1<br>Selection | CxA7 / GPIO_7<br>function | CxA6 / GPIO_6<br>function | CxB7 / GPIO_5<br>function | CxB6 / GPIO_4<br>function |

|------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| 0                      | CxA7                      | CxA6                      | CxB7                      | CxB6                      |

| 1                      | GPIO_7                    | GPIO_6                    | GPIO_5                    | GPIO_4                    |

Bit 6:

<u>CX GPIO 0</u>: Cx or I/O selection.

0 = CxA5, CxA4, CxB5 and CxB4 are used as sensor lines

1 = GPIO\_3, GPIO\_2, GPIO\_1 and GPIO\_0 are implemented as I/O's

| CX_GPIO_1<br>Selection | CxA5 / GPIO_3<br>function | CxA4 / GPIO_2<br>function | CxB5 / GPIO_1<br>function | CxB4 / GPIO_0<br>function |

|------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| 0                      | CxA5                      | CxA4                      | CxB5                      | CxB4                      |

| 1                      | GPIO_3                    | GPIO_2                    | GPIO_1                    | GPIO_0                    |

Table 1.9

Lower Nibble of I/O Port Selection

Please note that if the pins are selected as I/O's, then the TRIS and PORT can be configured as required. However if the pins are used as Cx sensors, then the TRIS MUST be set as inputs ('1') for those specific channels.

### *Bit 3-0:* <u>PM\_CX\_SELECT</u>: Groups who's Cx's are included in Prox Mode charging

0 = Group not included

1 = Group included

In this register, a selection of groups 4-1 is made to determine which sensor lines will be used during Prox Mode charging (Group 0). Each bit therefore represents four sensor lines to be added or removed from Group 0.

\*Note that at least two groups have to be set for this selection.

| Table 1.10 | Sensor Line Selection for Prox Mode |

|------------|-------------------------------------|

|------------|-------------------------------------|

| CX_CONFIG bit        | CH0  | CH1  | CH2  | СНЗ  |

|----------------------|------|------|------|------|

| 0 (Group 1 channels) | CxA0 | CxB0 | CxA4 | CxB4 |

| 1 (Group 2 channels) | CxA1 | CxB1 | CxA5 | CxB5 |

| 2 (Group 3 channels) | CxA2 | CxB2 | CxA6 | CxB6 |

| 3 (Group 4 channels) | CxA3 | CxB3 | CxA7 | CxB7 |

To help illustrate this, an example is provided. If bit 0 and 2 are set in CX\_CONFIG, the channels used in Prox Mode are shown in Table 1.11. It can be seen that the Proximity channel 0 (CH0) consists of the two sensor lines CxA0, and CxA2. And similarly the CH1 to CH3's sensor lines can be noted. This example thus has 8 of the 16 sensor lines also providing Proximity input. The other 8 have no influence on the Prox Mode channels.

#### Table 1.11 PM\_CX\_SELECT example

| CX_CONFIG      | CH0        | CH1        | CH2        | СНЗ        |

|----------------|------------|------------|------------|------------|

| CX_CONFIG= 05H | CxA0, CxA2 | CxB0, CxB2 | CxA4, CxA6 | CxB4, CxB6 |

It can be seen that if all 4 bits are set, all 16 of the Cx sensor lines are antenna inputs for the Prox Mode. It is recommended that if the design has any sensor buttons close to noise

sources (negative influence on proximity), that these can be chosen to fall in the same group, which can then be excluded from Prox Mode by means of the <u>PM\_CX\_SELECT</u> register.

#### Default Comms Pointer

The value stored in this register will be loaded into the Comms Pointer at the start of a communication window. For example, if the design only requires the Proximity Status information each cycle, then the <u>Default Comms Pointer</u> can be set to ADDRESS '31H'. This would mean that at the start of each communication window, the comms pointer would already be set to the <u>Proximity Status</u> register, simply allowing a READ to retrieve the data, without the need of setting up the address.

#### Individual Channel Disable

Each channel can be individually disabled in these registers. Note that the current group number has no influence on these registers as each channel disable register has a unique address.

#### Individual Channel Reseed

Each channel can be individually reseeded in these registers. Note that the current group number has no influence on these registers as each channel reseed register has a unique address. Also note that these bits are set initially by the IQS316 so that all channels are reseeded at startup, but are cleared immediately when each cycle is processed. However, the defaults are shown as '0', since after 1 cycle they are then cleared.

#### Auto-ATI Target

The automated ATI target can be set in these two consecutive registers. These registers are used for the Prox Mode, as well as the Touch Mode ATI targets. The selection between which of these modes to Auto-ATI, is set by <u>ATI\_MODE</u> in <u>UI\_SETTINGS0</u><6>.

For example, if the Prox Mode channels must be tuned to sample values = 800, and the Touch Mode channels to sample values = 400, the following steps are taken:

- Step 1: Set Auto ATI Target to 800

- Step 2: Select Prox Mode for ATI by clearing ATI\_MODE bit (<u>UI\_SETTINGS0</u><6> = 0)

- Step 3: Start Auto-ATI procedure by setting AUTO-ATI bit (<u>PROX\_SETTINGS\_1</u><3>)

- Step 4: Wait for Prox Mode ATI to complete, which is when <u>ATI\_BUSY</u> bit clears  $(UI_FLAGSO < 2 > = 0)$

- Step 5: Set Auto ATI Target to 400

- Step 6: Select Touch Mode for ATI by setting ATI\_MODE bit (<u>UI\_SETTINGS0</u><6> = 1)

- Step 7: Start Auto-ATI procedure by setting AUTO-ATI bit (<u>PROX\_SETTINGS\_1</u><3>)

#### I/O Port and Tris

When setup to be used as I/O's (<u>CX GPIO 1</u> and <u>CX GPIO 0</u> settings), the data direction can be set in the <u>I/O Tris</u> register as shown in Table 1.12.

If used as Cx's, the TRIS must be set as inputs!

|  | Table 1.12 | Tris | Config | uration |

|--|------------|------|--------|---------|

|--|------------|------|--------|---------|

| Tris bit<br><7:0> | I/O configuration |

|-------------------|-------------------|

| 0                 | Output            |

| 1                 | Input / Tri-state |

If setup as outputs, the state of the I/O's can then be set in the register as shown in Table 1.13

| Table 1           | .13 <b>I/O Outputs</b> |

|-------------------|------------------------|

| Port bit<br><7:0> | I/O status             |

| 0                 | Output LOW             |

| 1                 | Output HIGH            |

If setup as inputs, the status of the I/O's can be read from the register.

# **2** General Implementation hints

When implementing the communication interface with the IQS316, please refer to the IQS316 datasheet for a detailed description of the SPI and I<sup>2</sup>C communication. This section contains some general guidelines and hints regarding the communication interface.

## **2.1 Communication window**

Upon implementing either SPI or  $I^2C$  it is important to note the difference in the working of the communication window.

### 2.1.1 SPI Communication window

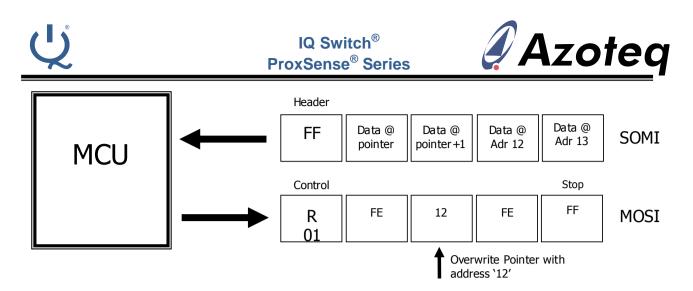

When communicating via SPI, the communication window will remain open until a new conversion command is received (FE written to IQS316 in 'address' time-slot of write transaction). While the communication window is open the master may initiate and terminate as many read and write communication sessions as required.

#### 2.1.2 I<sup>2</sup>C Communication window

When communicating via  $I^2C$ , the communication window will automatically close when an  $I^2C$  STOP bit is received by the IQS316. The IQS316 will then proceed to start with a new conversion and the READY line will be pulled low until the new conversion is complete.

Note that there is no command via  $I^2C$  to initiate a new conversion. To perform multiple read and write commands, the repeated start function of the  $I^2C$  must be used to stack the commands together.

# 2.2 Startup Procedure

The following procedures are for setup of specific features of the IQS316 that requires more attention. More features can be setup by setting the appropriate registers as required.

### 2.2.1 Individual Prox and Touch Thresholds

- Step 1: First set <u>PROX\_SETTINGS\_2</u><3> to skip conversion. This will ensure that the system always cycles through all the groups.

- Step 2: Read the group number from the <u>GROUP\_NUM</u> register (3Dh).

- Step 3: In a 'switch' construct, check which group number was read.

- Step 4: For this group set the thresholds by writing the chosen threshold values bits 7-4 of 83h, 85h, 87h or 89h, depending on the group number. Remember the threshold values are also determined by the Prox range bit, <u>UI\_SETTINGS0</u><5>, which will set the range for <u>all</u> the groups.

- Step 5: End the I<sup>2</sup>C window and allow for small delay. No conversions will take place but the group number will increment.

- Step 6: Read the group number again, and repeat Steps 3-5 until all the groups 0 to 4 has been configured.

- Step 7: Make sure to disable skip conversions so that sensing can resume.

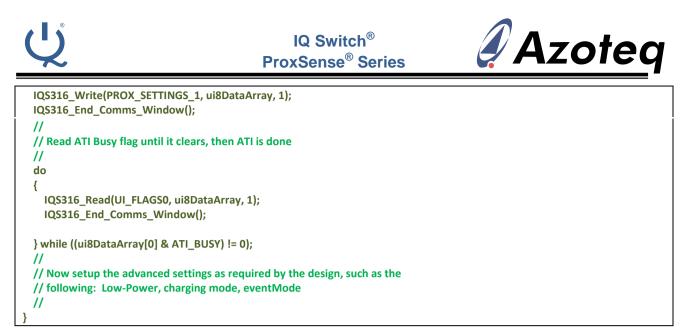

### 2.2.2 Auto ATI Procedure

For example, if the Prox Mode channels must be tuned to sample values = 800, and the Touch Mode channels to sample values = 400. It is necessary to force the IQS316 to Prox- or touch-mode during setup of the auto ATI. The following steps are taken:

- Step 1: Set Auto ATI Target to 800

- Step 2: Select Prox Mode for ATI by clearing ATI\_MODE bit (<u>UI\_SETTINGS0</u><6> = 0), here it is crucial to end the communication window so that the next cycle is in Prox Mode.

- Step 3: Start Auto-ATI procedure by setting AUTO-ATI bit (<u>PROX\_SETTINGS\_1</u><3>)

- Step 4: Wait for Prox Mode ATI to complete, which is when <u>ATI\_BUSY</u> bit clears  $(UI_FLAGSO<2>=0)$

- Step 5: Set Auto ATI Target to 400

- Step 6: Select Touch Mode for ATI by setting ATI\_MODE bit (<u>UI\_SETTINGS0</u><6> = 1), here it is crucial to end the communication window so that the next cycle is in Prox Mode.

- Step 7: Start Auto-ATI procedure by setting AUTO-ATI bit (<u>PROX\_SETTINGS\_1</u><3>)

- Step 8: Wait for Touch Mode ATI to complete, which is when <u>ATI\_BUSY</u> bit clears (UI FLAGSO < 2 > = 0)

Although the ATI is finished, the current samples will take a few conversions to settle at the correct value.

### 2.2.3 Post Setup

After sending initial settings to the IQS316, it is recommended to execute a reseed. If the Auto ATI was done last, it may not be necessary to reseed.

# 2.3 General I<sup>2</sup>C Hints

### 2.3.1 I<sup>2</sup>C Pull-up resistors

When implementing  $I^2C$  it is important to remember the pull-up resistors on the data and clock lines. 4.7k $\Omega$  is recommended, but for lower clock speeds bigger pull-ups will reduce power consumption.

#### 2.3.2 MCLR

Suggested implementation is to have the IQS316 and the pull-up resistors connect to the power supply of the device. The MCLR pin should then be used to reset the IQS316. Remember to hold the MCLR low until master setup has been done.

### 2.3.3 Reset Device while using I<sup>2</sup>C

When a reset occurs, some care needs to be taken to ensure that the IQS316 restarts correctly. The reset pin needs to be LOW before the IQS316 can be initialised, otherwise the master will read a ready signal prematurely. To accomplish this without any delays, define the ready pin on the master as an output and pull it LOW. Then, redefine it as an input line just before initializing the IQS316.

# **3** Sample implementation

An example implementation of the IQS316 is described in this section. This implementation performs a setup of the IQS316, and then retrieves Prox and touch data for each cycle. For this implementation a PIC18F4550 was used as the master device.

Communication between the master and the IQS316 was done in SPI and for  $I^2C$ , and are both covered in this section. For further explanations of the  $I^2C$  and SPI protocol, refer to the IQS316 datasheet.

The example implementation firmware was done in MPLAB X version 1.85.

The compiler used was C18 version 3.46.

Complete projects for SPI and  $I^2C$  are available for reference.

### 3.1 Overview

- Firstly an initialisation function configures the PIC microcontroller

- Then the communication is configured (either SPI or I<sup>2</sup>C) for communication between the PIC and the IQS316. (NOTE: the selection between SPI and I<sup>2</sup>C must be done separately in hardware on the IQS316 PCB by correctly configuring the SPI\_SELECT)

- A delay is added to allow the IQS316 to start up correctly (the datasheet says 16ms can be expected until RDY is active for the first time)

- Now the settings on the IQS316 are configured via I<sup>2</sup>C or SPI

- The setup is now completed and the system enters an endless loop where new data is obtained from the IQS316, and then processed.

### **3.1.1 Communications:**

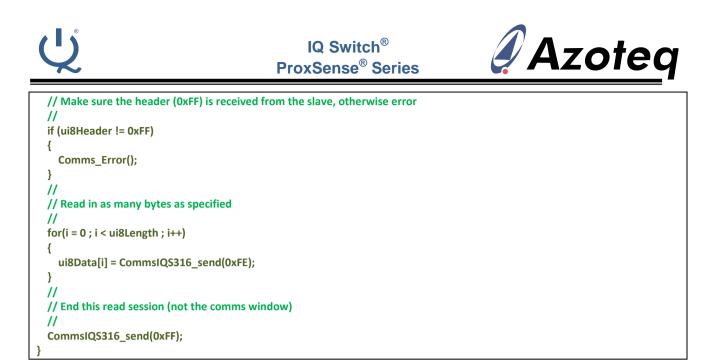

For a detailed description of the communication protocol refer to the IQS316 datasheet.

SPI:

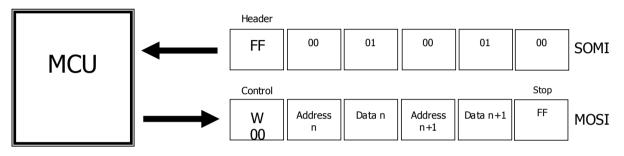

*Writing to IQS316:* The master initiates communication by writing a zero (00H) to the IQS316. Next the address to write is sent to the IQS316. The byte sent after the address will be written to that address.

Another address can now be sent to the IQS316. Communication is terminated by sending FFH instead of an address. (This only ends the transaction, and not the current communication window)

E.g. write 35H to address 12H:

Master writes 00H to IQS316. (Initiates comms in write mode, FFH returned)

Master writes 12H to IQS316. (Setup address, returns 00H)

Master writes 35H to IQS316. (35H stored at address 12H, 01H returned)

Master writes FFH to IQS316. (End write cycle, 00H returned)

Additionally, if the master writes FEH to the IQS316, a new conversion will be initiated and the communication window will be terminated.